Note

EE-341

更多关于ADI公司的DSP、处理器以及开发工具的技术资料,

请访问网站:/ee-note和/processor如需技术支持,请发邮件至processor.support@或processor.tools.support@

Blackfin®专用管脚复用插件

作者:JagadeeshRayala

Rev1-May15,2008

简介

本文介绍了如何使用VisualDSP++®开发工具(5.0或更高版本的专用管脚复用插件来配置ADSP-BF54x和ADSP-BF52x的端口寄存器。

使用管脚复用插件可以自动生成C或汇编代码来配置端口寄存器,这样可以大大降低工作量。

管脚复用 ADSP-BF52x和ADSP-BF54x系列Blackfin处理器具有一系列丰富的外设,通过强大的管脚复用机制,为外部应用空间提供很高的灵活性。

因为具有一系列丰富的外设端口,ADSP-BF52x处理器将这些外设信号分成四个端口组,分别为PORTF,PORTG,PORTH,PORTJ。

对于ADSP-BF54x来说,外设信号被分成了十个端口组,从PORTA到PORTJ。

大多数相关管脚可以被多路信号来共享。

通过多路复用器控制端口的功能。

PORTA到PORTJ的每个管脚(ADSP-BF52x处理器的PORTF,PORTG,PORTH)还能作为通用的输入输出管脚。

任何没有被外设功能占用的管脚都可以单独地被配置成GPIO模式。

在默认的情况下,重启以后的所有管脚都是GPIO模式。

但是GPIO的输入输出驱动在默认设置中都是未激活的。

每个端口都有一套自己的映射到内存的寄存器,用于控制端口复用和GPIO功能。

使用外设功能需要明确的使能寄存器(PORTx_FER,对于ADSP-BF52x此处x表示

F,G,H)。

端口里面外设间的复用由另一个多路控制寄存器来控制(PORTx_MUX)。

如果清除PORTx_FER的相应位,任何管脚都可以被单独地设置成GPIO功能来取代外设功能。

如果要把管脚设置为GPIO输出模式,必须设置好PORTxIO_DIR寄存器中相应的方向位(ADSP-BF54x处理器中对应为PORTx_DIR_SET)。

为了使用管脚的数字输入功能,需要使能PORTxIO_INEN寄存器(ADSP-BF54x对应为PORTx_INEN)。

默认情况下,所有的外设管脚在重启后都是被配置为输入模式。

但是,为减小功耗或者减少无用管脚外部上拉电阻的数量,GPIO输入驱动器也可以被关闭。

关于管脚复用的更多信息,请参考处理器的硬件参考手册[1][2]。

对于外设和GPIO的配置,需要对下列信息有深入的了解,端口寄存器,所有寄存器中不同的bit域对应不同的信号,所有寄存器各bit域中占用的bit数,以及所有寄存器中不同数值对应的不同信号。

Copyright2008,AnalogDevices,Inc.Allrightsreserved.AnalogDevicesassumesnoresponsibilityforcustomerproductdesignortheuseorapplicationofcustomers’productsorforanyinfringementsofpatentsorrightsofotherswhichmayresultfromAnalogDevices’assistance.Alltrademarksandlogosarepropertyoftheirrespectiveholders.InformationfurnishedbyAnalogDevices’applicationsanddevelopmenttoolsengineersisbelievedtobeurateandreliable,howevernoresponsibilityisassumedbyAnalogDevicesregardingtechnicaluracyicalityofthecontentprovidedinAnalogDevices’Engineer-to-EngineerNotes. 专用的管脚复用插件为生成端口寄存器的配置代码提供了简便方法。

这个专用的管脚复用工具使你能够无需考虑内部细节就能生成所需代码。

专用管脚复用插件工具的安装 在VisualDSP++5.0环境下安装专用管脚复用插件:

1.从附带的.zip文件(EE341v01.zip)中解压提取出ExpertPinMux.dll文件,放置到VisualDSP++的 system文件夹下。

如果VisualDSP是安装在C盘(默认安装路径),复制附带文件到如下文件夹:C:\ProgramFiles\AnalogDevice\VisualDSP5.0\System2.输入下列命令行注册ExpertPinMux.dllC:\Windows\system32\regsvr32.exeExpertPinMux.dll必须在<安装路径>\System文件夹,而不是根目录下运行regsvr32.exe。

现在,专用管脚复用工具能在Preferences对话框(settings->Preferences)中的Plugins页下显示了。

通过Tools目录便可以访问专用管脚复用实体。

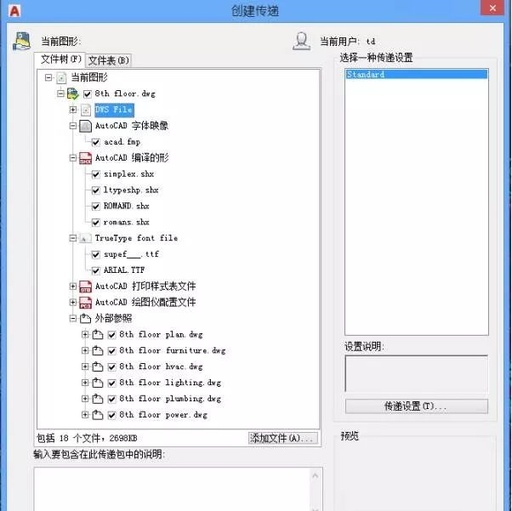

此插件只能工作在VisualDSP++5.0或更高版本的ADSP-BF52x和ADSP-BF54x环境下 图1显示了默认状态下的专用管脚复用窗口。

默认设置下,ADSP-BF522处理器处于选中状态,所有列表框按照选中状态显示。

图1专用管脚复用窗口Blackfin®专用管脚复用插件(EE-341) 第2页,共10页 专用管脚复用插件的使用 生成代码:

1.在ProcessorSelection中,选择需要生成代码的处理器型号。

2.在PeripheralSelection下,选择所需的外设模块。

当外设模块被选中,SignalSelection列表框根据所选外设模块显示出所有相关的信号。

3.添加一个外设信号,在SignalSelection列表框中选择相应信号并双击。

图2配置受限的外设信号时,消息中心显示错误详情 当外设信号添加完成,PeripheralConfiguration列表框将进行相应更新。

一旦外设信号添加完成,所有和该配置信号复用的信号(包括外设的和GPIO)在此后的配置中将受到工具的限制。

工具为这些受限信号提供可视的提示,在这些信号名称上附加“*”。

例如,在ADSP-BF527上配置PPID12。

当PPID12与DT1PRI,SPISEL2以及PF12复用时,所有四个信号的名字上方都附加了一个“*”。

注意,即使在PPID13没有配置的情况下,TSCLK1和SPISEL3的信号名称上也会附加上“*”。

Blackfin®专用管脚复用插件(EE-341) 第3页,共10页 这是因为这两个信号(PPID12和PPID13)属于同一个复用组。

如果一个受限信号被配置了,消息中心对话框将会显示错误消息。

图2显示了在配置了PPID12的情况下试图配置TSCLK1*时,消息中心对话框中显示的错误消息。

4.GPIO管脚可以在GPIODirectionSelection列表中选择。

点击ConfigureasInput或者ConfigureasOutput按钮可以分别将GPIO管脚设置成输入或输出。

图3消息中心显示关于配置受限的GPIO信号的错误详情 添加了GPIO信号后,GPIOConfiguration列表将相应地进行更新。

一旦GPIO信号被添加,工具就将限制所有与此GPIO管脚复用的其它信号的配置。

如果GPIO管脚已经被配置为输出,工具还将限制把它配置成输出的操作,反之亦然。

例如,在ADSP-BF549的CZM已经被配置的情况下,因为CZM与SPI1SEL1,HOST_CE,PPI2_FS2以及PG5复用,所有这五个信号名称上都将被附加“*”。

如图

3,显示了当CZM配置完成后试图将PG5*配置成输出时,消息中心对话框产生的错误消息。

5.重复步骤2到

4,添加应用或系统设计中所有相关的外设信号或GPIO。

注意:对于外设和GPIO信号的配置是没有顺序限制的。

Blackfin®专用管脚复用插件(EE-341) 第4页,共10页

6.选中恰当的选项,点击GenerateCode按钮生成C和/或汇编代码。

这个操作将打开一个对话框,要求你为生成的C或汇编代码选择存放路径以及文件名称。

默认情况下,生成代码将以pin.c或pin.asm命名。

如果更换处理器型号,PeripheralConfiguration和GPIOConfiguration中的数据将自动清除。

同时,PeripheralSelection,SignalSelection和GPIODirectionSelection框中的信号将根据所选处理器进行更新。

选中要删除的信号,点击Delete按钮来撤销对外设信号或者GPIO输入/输出管脚的配置。

所有的列表对话框也将相应地更新。

专用管脚复用插件还提供以下功能: 保存配置。

点击SaveConfiguration按钮保存以下所有信息:当前选定的处理器/外设/信号/GPIO,外设信号/GPIO的配置,Messagecenter对话框内容以及每个列表和选择对话框中的当前状态。

所有信息保存在扩展名为.cfg的输出文件中(pin.cfg是其默认名字)。

载入配置。

点击LoadConfiguration按钮载入保存的配置(.cfg文件)。

按照提示选择一个.cfg文件。

选择好。

cfg文件后,ExpertPinMultiplexing窗口将更新,显示.cfg文件中的内容。

此时可以为每个新设计添加或删除外设/GPIO信号,重新生成代码。

代码生成 本节将通过一个例子来说明生成代码的过程。

假设一个基于ADSP-BF522的应用,按照以下要求配置外设信号以及GPIO: 外设□SPORT(DR1PRI,DT1PRT,RFS1,RSCLK1,TFS1和TSCLK1)□UART0(UART0RX和UART0TX)□HOST(HOST_ACK,HOST_ADDR,HOST_CE,HOST_RD,HOST_WR以及HOST_Dx:x=0到15)□从模式下的SPI(MISO,MOSI,SCK和SPISS) GPIO□输入(PF3和PF5)□输出(PF1和PG10) 图4示范了按照上述配置生成控制端口寄存器的C和汇编代码过程。

生成的汇编和C代码分别在附录的列表1和列表2中。

将生成的C/汇编代码添加到VisualDSP++工程中。

C语言工程,主函数需要调用InitPorts()函数。

汇编工程中,主程序调用_InitPorts子程序。

Blackfin®专用管脚复用插件(EE-341) 第5页,共10页 图4生成配置ADSP-BF522处理器端口寄存器的C和汇编代码 Blackfin®专用管脚复用插件(EE-341) 第6页,共10页 附录 Pin.asm /*AssemblycodegeneratedtoconfigurePORTsandGPIOs. Peripheralpinsselected:DR1PRI,DT1PRI,HOST_ACK,HOST_ADDR,HOST_CE,HOST_D0,HOST_D1,HOST_D10,HOST_D11,HOST_D12,HOST_D13,HOST_D14,HOST_D15,HOST_D2,HOST_D3,HOST_D4,HOST_D5,HOST_D6,HOST_D7,HOST_D8,HOST_D9,HOST_RD,HOST_WR,MISO,MOSI,RFS1,RSCLK1,SCK,SPISS,TFS1,TSCLK1,UART0RX,UART0TX GPIOsconfiguredasInputs:PF3,PF5 GPIOsconfiguredasOutputs:PF1,PG10*/ #include//ThisfunctionwillsetupthePortControlRegisters.sectionprogram;.global_InitPorts;

_InitPorts://Firstsaveregisters[--sp]=rets;[--sp]=p0;[--sp]=r0;

//PORTx_MUXregistersp0.l=lo(PORTF_MUX);p0.h=hi(PORTF_MUX);r0.l=0x154;w[p0]=r0;

p0.l=lo(PORTG_MUX);p0.h=hi(PORTG_MUX);r0.l=0x2820;w[p0]=r0;

p0.l=lo(PORTH_MUX);p0.h=hi(PORTH_MUX);r0.l=0x2a;w[p0]=r0;

//PORTx_FERregistersp0.l=lo(PORTF_FER);p0.h=hi(PORTF_FER);r0.l=0x3f00;w[p0]=r0;

p0.l=lo(PORTG_FER);p0.h=hi(PORTG_FER);r0.l=0xf99e;

Blackfin®专用管脚复用插件(EE-341)

第7页,共10页

w[p0]=r0;

p0.l=lo(PORTH_FER);p0.h=hi(PORTH_FER);r0.l=0xffff;w[p0]=r0;

//PORTxIO_DIRregistersp0.l=lo(PORTFIO_DIR);p0.h=hi(PORTFIO_DIR);r0.l=0x2;w[p0]=r0;

p0.l=lo(PORTGIO_DIR);p0.h=hi(PORTGIO_DIR);r0.l=0x400;w[p0]=r0;

p0.l=lo(PORTHIO_DIR);p0.h=hi(PORTHIO_DIR);r0.l=0x0;w[p0]=r0;

//PORTxIO_INENregistersp0.l=lo(PORTFIO_INEN);p0.h=hi(PORTFIO_INEN);r0.l=0x28;w[p0]=r0;

p0.l=lo(PORTGIO_INEN);p0.h=hi(PORTGIO_INEN);r0.l=0x0;w[p0]=r0;

p0.l=lo(PORTHIO_INEN);p0.h=hi(PORTHIO_INEN);r0.l=0x0;w[p0]=r0;

//Restoretheregistersr0=[sp++];p0=[sp++];rets=[sp++];

//Returnbackfromthesubroutinerts;

列表1pin.asm

Blackfin®专用管脚复用插件(EE-341)

第8页,共10页

pin.c

/*CcodegeneratedtoconfigurePORTsandGPIOs.

Peripheralpinsselected:DR1PRI,DT1PRI,HOST_ACK,HOST_ADDR,HOST_CE,HOST_D0,HOST_D1,HOST_D10,HOST_D11,HOST_D12,HOST_D13,HOST_D14,HOST_D15,HOST_D2,HOST_D3,HOST_D4,HOST_D5,HOST_D6,HOST_D7,HOST_D8,HOST_D9,HOST_RD,HOST_WR,MISO,MOSI,RFS1,RSCLK1,SCK,SPISS,TFS1,TSCLK1,UART0RX,UART0TX

GPIOsconfiguredasInputs:PF3,PF5

GPIOsconfiguredasOutputs:PF1,PG10*/

#include

voidInitPorts();

//ThisfunctionwillsetupthePortControlRegistersvoidInitPorts(){

//FirstSetPORTx_MUXregisters*pPORTF_MUX=0x154;*pPORTG_MUX=0x2820;*pPORTH_MUX=0x2a;

//SetPORTx_FERregisters*pPORTF_FER=0x3f00;*pPORTG_FER=0xf99e;*pPORTH_FER=0xffff;

//SetPORTxIO_DIRregisters*pPORTFIO_DIR=0x2;*pPORTGIO_DIR=0x400;*pPORTHIO_DIR=0x0;

//SetPORTxIO_INENregisters*pPORTFIO_INEN=0x28;*pPORTGIO_INEN=0x0;*pPORTHIO_INEN=0x0;}

列表2pin.c

Blackfin®专用管脚复用插件(EE-341)

第9页,共10页

参考文献

[1]ADSP-BF52xBlackfinProcessorHardwareReference(Volume1of2).Rev0.3(Preliminary),September2007.AnalogDevices,Inc.

[2]ADSP-BF54xBlackfin®ProcessorHardwareReference.Rev0.2,September2007.AnalogDevices,Inc.

[3]ADSP-BF522/523/524/525/526/527Blackfin®EmbeddedProcessorPreliminaryDataSheet.RevPrD,December2007.AnalogDevices,Inc.

[4]ADSP-BF542/BF544/BF547/BF548/BF549Blackfin®EmbeddedProcessorPreliminaryDataSheet.RevPrG,December2007.AnalogDevices,Inc.

文档记录

Revision

Rev1–May15,2008R.Jagadeesh

DescriptionInitialrelease.

Blackfin®专用管脚复用插件(EE-341)

第10页,共10页

使用管脚复用插件可以自动生成C或汇编代码来配置端口寄存器,这样可以大大降低工作量。

管脚复用 ADSP-BF52x和ADSP-BF54x系列Blackfin处理器具有一系列丰富的外设,通过强大的管脚复用机制,为外部应用空间提供很高的灵活性。

因为具有一系列丰富的外设端口,ADSP-BF52x处理器将这些外设信号分成四个端口组,分别为PORTF,PORTG,PORTH,PORTJ。

对于ADSP-BF54x来说,外设信号被分成了十个端口组,从PORTA到PORTJ。

大多数相关管脚可以被多路信号来共享。

通过多路复用器控制端口的功能。

PORTA到PORTJ的每个管脚(ADSP-BF52x处理器的PORTF,PORTG,PORTH)还能作为通用的输入输出管脚。

任何没有被外设功能占用的管脚都可以单独地被配置成GPIO模式。

在默认的情况下,重启以后的所有管脚都是GPIO模式。

但是GPIO的输入输出驱动在默认设置中都是未激活的。

每个端口都有一套自己的映射到内存的寄存器,用于控制端口复用和GPIO功能。

使用外设功能需要明确的使能寄存器(PORTx_FER,对于ADSP-BF52x此处x表示

F,G,H)。

端口里面外设间的复用由另一个多路控制寄存器来控制(PORTx_MUX)。

如果清除PORTx_FER的相应位,任何管脚都可以被单独地设置成GPIO功能来取代外设功能。

如果要把管脚设置为GPIO输出模式,必须设置好PORTxIO_DIR寄存器中相应的方向位(ADSP-BF54x处理器中对应为PORTx_DIR_SET)。

为了使用管脚的数字输入功能,需要使能PORTxIO_INEN寄存器(ADSP-BF54x对应为PORTx_INEN)。

默认情况下,所有的外设管脚在重启后都是被配置为输入模式。

但是,为减小功耗或者减少无用管脚外部上拉电阻的数量,GPIO输入驱动器也可以被关闭。

关于管脚复用的更多信息,请参考处理器的硬件参考手册[1][2]。

对于外设和GPIO的配置,需要对下列信息有深入的了解,端口寄存器,所有寄存器中不同的bit域对应不同的信号,所有寄存器各bit域中占用的bit数,以及所有寄存器中不同数值对应的不同信号。

Copyright2008,AnalogDevices,Inc.Allrightsreserved.AnalogDevicesassumesnoresponsibilityforcustomerproductdesignortheuseorapplicationofcustomers’productsorforanyinfringementsofpatentsorrightsofotherswhichmayresultfromAnalogDevices’assistance.Alltrademarksandlogosarepropertyoftheirrespectiveholders.InformationfurnishedbyAnalogDevices’applicationsanddevelopmenttoolsengineersisbelievedtobeurateandreliable,howevernoresponsibilityisassumedbyAnalogDevicesregardingtechnicaluracyicalityofthecontentprovidedinAnalogDevices’Engineer-to-EngineerNotes. 专用的管脚复用插件为生成端口寄存器的配置代码提供了简便方法。

这个专用的管脚复用工具使你能够无需考虑内部细节就能生成所需代码。

专用管脚复用插件工具的安装 在VisualDSP++5.0环境下安装专用管脚复用插件:

1.从附带的.zip文件(EE341v01.zip)中解压提取出ExpertPinMux.dll文件,放置到VisualDSP++的 system文件夹下。

如果VisualDSP是安装在C盘(默认安装路径),复制附带文件到如下文件夹:C:\ProgramFiles\AnalogDevice\VisualDSP5.0\System2.输入下列命令行注册ExpertPinMux.dllC:\Windows\system32\regsvr32.exeExpertPinMux.dll必须在<安装路径>\System文件夹,而不是根目录下运行regsvr32.exe。

现在,专用管脚复用工具能在Preferences对话框(settings->Preferences)中的Plugins页下显示了。

通过Tools目录便可以访问专用管脚复用实体。

此插件只能工作在VisualDSP++5.0或更高版本的ADSP-BF52x和ADSP-BF54x环境下 图1显示了默认状态下的专用管脚复用窗口。

默认设置下,ADSP-BF522处理器处于选中状态,所有列表框按照选中状态显示。

图1专用管脚复用窗口Blackfin®专用管脚复用插件(EE-341) 第2页,共10页 专用管脚复用插件的使用 生成代码:

1.在ProcessorSelection中,选择需要生成代码的处理器型号。

2.在PeripheralSelection下,选择所需的外设模块。

当外设模块被选中,SignalSelection列表框根据所选外设模块显示出所有相关的信号。

3.添加一个外设信号,在SignalSelection列表框中选择相应信号并双击。

图2配置受限的外设信号时,消息中心显示错误详情 当外设信号添加完成,PeripheralConfiguration列表框将进行相应更新。

一旦外设信号添加完成,所有和该配置信号复用的信号(包括外设的和GPIO)在此后的配置中将受到工具的限制。

工具为这些受限信号提供可视的提示,在这些信号名称上附加“*”。

例如,在ADSP-BF527上配置PPID12。

当PPID12与DT1PRI,SPISEL2以及PF12复用时,所有四个信号的名字上方都附加了一个“*”。

注意,即使在PPID13没有配置的情况下,TSCLK1和SPISEL3的信号名称上也会附加上“*”。

Blackfin®专用管脚复用插件(EE-341) 第3页,共10页 这是因为这两个信号(PPID12和PPID13)属于同一个复用组。

如果一个受限信号被配置了,消息中心对话框将会显示错误消息。

图2显示了在配置了PPID12的情况下试图配置TSCLK1*时,消息中心对话框中显示的错误消息。

4.GPIO管脚可以在GPIODirectionSelection列表中选择。

点击ConfigureasInput或者ConfigureasOutput按钮可以分别将GPIO管脚设置成输入或输出。

图3消息中心显示关于配置受限的GPIO信号的错误详情 添加了GPIO信号后,GPIOConfiguration列表将相应地进行更新。

一旦GPIO信号被添加,工具就将限制所有与此GPIO管脚复用的其它信号的配置。

如果GPIO管脚已经被配置为输出,工具还将限制把它配置成输出的操作,反之亦然。

例如,在ADSP-BF549的CZM已经被配置的情况下,因为CZM与SPI1SEL1,HOST_CE,PPI2_FS2以及PG5复用,所有这五个信号名称上都将被附加“*”。

如图

3,显示了当CZM配置完成后试图将PG5*配置成输出时,消息中心对话框产生的错误消息。

5.重复步骤2到

4,添加应用或系统设计中所有相关的外设信号或GPIO。

注意:对于外设和GPIO信号的配置是没有顺序限制的。

Blackfin®专用管脚复用插件(EE-341) 第4页,共10页

6.选中恰当的选项,点击GenerateCode按钮生成C和/或汇编代码。

这个操作将打开一个对话框,要求你为生成的C或汇编代码选择存放路径以及文件名称。

默认情况下,生成代码将以pin.c或pin.asm命名。

如果更换处理器型号,PeripheralConfiguration和GPIOConfiguration中的数据将自动清除。

同时,PeripheralSelection,SignalSelection和GPIODirectionSelection框中的信号将根据所选处理器进行更新。

选中要删除的信号,点击Delete按钮来撤销对外设信号或者GPIO输入/输出管脚的配置。

所有的列表对话框也将相应地更新。

专用管脚复用插件还提供以下功能: 保存配置。

点击SaveConfiguration按钮保存以下所有信息:当前选定的处理器/外设/信号/GPIO,外设信号/GPIO的配置,Messagecenter对话框内容以及每个列表和选择对话框中的当前状态。

所有信息保存在扩展名为.cfg的输出文件中(pin.cfg是其默认名字)。

载入配置。

点击LoadConfiguration按钮载入保存的配置(.cfg文件)。

按照提示选择一个.cfg文件。

选择好。

cfg文件后,ExpertPinMultiplexing窗口将更新,显示.cfg文件中的内容。

此时可以为每个新设计添加或删除外设/GPIO信号,重新生成代码。

代码生成 本节将通过一个例子来说明生成代码的过程。

假设一个基于ADSP-BF522的应用,按照以下要求配置外设信号以及GPIO: 外设□SPORT(DR1PRI,DT1PRT,RFS1,RSCLK1,TFS1和TSCLK1)□UART0(UART0RX和UART0TX)□HOST(HOST_ACK,HOST_ADDR,HOST_CE,HOST_RD,HOST_WR以及HOST_Dx:x=0到15)□从模式下的SPI(MISO,MOSI,SCK和SPISS) GPIO□输入(PF3和PF5)□输出(PF1和PG10) 图4示范了按照上述配置生成控制端口寄存器的C和汇编代码过程。

生成的汇编和C代码分别在附录的列表1和列表2中。

将生成的C/汇编代码添加到VisualDSP++工程中。

C语言工程,主函数需要调用InitPorts()函数。

汇编工程中,主程序调用_InitPorts子程序。

Blackfin®专用管脚复用插件(EE-341) 第5页,共10页 图4生成配置ADSP-BF522处理器端口寄存器的C和汇编代码 Blackfin®专用管脚复用插件(EE-341) 第6页,共10页 附录 Pin.asm /*AssemblycodegeneratedtoconfigurePORTsandGPIOs. Peripheralpinsselected:DR1PRI,DT1PRI,HOST_ACK,HOST_ADDR,HOST_CE,HOST_D0,HOST_D1,HOST_D10,HOST_D11,HOST_D12,HOST_D13,HOST_D14,HOST_D15,HOST_D2,HOST_D3,HOST_D4,HOST_D5,HOST_D6,HOST_D7,HOST_D8,HOST_D9,HOST_RD,HOST_WR,MISO,MOSI,RFS1,RSCLK1,SCK,SPISS,TFS1,TSCLK1,UART0RX,UART0TX GPIOsconfiguredasInputs:PF3,PF5 GPIOsconfiguredasOutputs:PF1,PG10*/ #include

声明:

该资讯来自于互联网网友发布,如有侵犯您的权益请联系我们。