FX2LP™GPIF入门

AN66806

作者名称:RamaSaiKrishnaVakkantula关联项目:有

软件版本:KeiluVision2,GPIFDesigner要获取完整的应用笔记列表,请单击此处。

更多示例代码?

我们听到了。

要获取更多USBHi-Speed示例代码,请访问网站。

FX2LP™通用可编程接口(GPIF)提供一个独立硬件单元,用于创建数据和控制外部接口所需要的信号。

通过对GPIF寄存器进行CPU读和写操作,GPIF可以移位数据。

本文档通过提供一个简单设计(该设计对GPIF时钟进行2、4和7分频)详细介绍了GPIF单元和它的图形设计工具(称为GPIFDesigner)。

在配置和管理该接口时,仅需要三行C代码。

本应用笔记还提供了一个示例,用于演示了如何将USB连接添加到GPIF设计。

目录 1简介..........................................................................12FX2LP架构概述.......................................................2 2.1端口模式..........................................................22.2从设备FIFO模式.............................................22.3GPIF模式—自动............................................22.4GPIF模式—手动............................................33通用可编程接口........................................................33.1GPIF概述........................................................33.2物理互连..........................................................44创建一个GPIF应用..................................................54.1设计GPIF接口................................................54.2使用固件框架...................................................54.3使用GPIFDesigner实现GPIF波形................65示例1:对GPIF时钟进行2分频和4分频...............66示例2:对GPIF时钟进行7分频...........................167示例3:使用单个字的读/写数据操作......................18 8USB数据流............................................................21 9设计GPIF互联.......................................................21 9.1单字写波形.....................................................23 9.2单字读波形.....................................................27 9.3单个字操作的固件编程...................................30 9.4代码段............................................................31 9.5运行GPIF单个字操作示例............................36 9.6单个字操作的逻辑分析仪波形........................37 10 相关文档.............................................................39 10.1其他GPIF示例..............................................39 10.2参考设计........................................................39 10.3数据手册........................................................39 11 总结....................................................................39 文档修订记录...................................................................40 全球销售和设计支持........................................................41 1简介 USB2.0的480Mbps信号速率要求控制器芯片对高速数据进行输出/输入传输。

提供了一个独立的硬件单元,CPU通过对其进行相关设置实现USB端点FIFO和外部接口之间的数据直接传输。

外部接口可以是RAM、FIFO或第二个处理器。

因此,CPU不需要移动数据。

配置时,由于数据经过了GPIF硬件通道,因此CPU仅控制各标志和中断。

通过使用GPIF可以实现各种协议,包括增强型IDE(EIDE–有时成为快速ATA或快速IDE)或ATA数据接口(ATAPI)打印机,并行接口(IEEEP1284),以及ia.ThisdocumentdescribesthearchitectureandimplementationoftheFX2LPGPIF.本文档对FX2LPGPIF的架构和实现进行了说明。

介绍了应用使用模型和调试决策,并提供了各种示例用于介绍和解释GPIF概念。

文档编号.001-92462版本.*

A 1 EZ-USB®FX2LP™GPIF入门 2FX2LP架构概述 EZ-USBFX2LP是一个灵活的USB2.0外设控制器,用于处理USB2.0的最大宽度。

FX2LP通过提供GPIF为外部器件提供高速并行接口,从而优化USB的吞吐量。

通过使用该GPIF,可以在FX2LP端点FIFO和GPIF接口间传输数据。

以下各节通过提供可配置的不同FX2LP模式,对FX2LP架构进行了简要说明。

2.1端口模式 FX2LP拥有24个接口引脚,根据模式设置,可将这些引脚用于各种目的。

在“端口”模式下,它们是通用的I/O引脚,并且GPIF无效(图1)。

图

1.端口模式下的FX2LP Host(PC) USBSIE FIFOs 8051 FX2LP Pins PA[7:0]PB[7:0]PD[7:0] 2.2从设备FIFO模式 在从设备FIFO模式中,专用的FX2LP逻辑提供了控制和数据信号,用于将USB端点FIFO连接到外部FIFO控制器。

除了数据总线和FIFO选择输入外,该接口还提供了常用的FIFO信号,如RD、WR和FIFO标志。

更多有关该接口的详细信息,请参考赛普拉斯应用笔记AN63787-EZ-USBFX2LPGPIFandSlaveFIFOConfigurationExamplesUsing8-bitAsynchronousInterface. 图

2.从设备FIFO模式下的FX2LP引脚 Host(PC) USBSIE FIFOs 8051 FX2LP Pins SlaveFIFOlogic CLKRD,WRFLAGS DATA[15:0]ADDR[1:0] Control 2.3GPIF模式—自动 当GPIF有效时,接口引脚作为主设备控制外部外设,如RAM、FIFO或外部处理器。

GPIF可在两个子模式下运行:自动模式和手动模式。

在自动模式下,数据从端点FIFO直接输送到外部接口。

8051配置和监控该接口,但不会直接访问FIFO数据;请参考图

3. 图

3.GPIF自动模式下的FX2LP Host(PC) USBSIE FIFOs 8051 FX2LP PinsGPIF IFCLKCTL[5:0]ADDR[8:0]DATA[15:0]RDY[5:0]Gstate[2:0] 文档编号.001-92462版本.*

A 2 EZ-USB®FX2LP™GPIF入门 赛普拉斯应用笔记AN57322-InterfacingSRAMwithFX2LPoverGPIF来说明GPIF自动模式。

该笔记介绍了如何使用8位异步接口和GPIF自动模式将赛普拉斯CY7C1399BSRAM连接至FX2LP。

2.4GPIF模式—手动 在手动模式下,通过使用GPIF寄存器的读和写操作,8051对该接口进行读写字节(图4)。

在本文档的后续内容中介绍了GPIF手动模式的一个示例。

示例3:使用单个字的读/写数据操作. 图

4.GPIF手动模式下的FX2LP Host(PC) USBSIE FIFOs 8051 FX2LP PinsGPIF IFCLKCTL[5:0]ADDR[8:0]DATA[15:0]RDY[5:0]Gstate[2:0] 3通用可编程接口 3.1GPIF概述 GPIF的内核是一个可编程状态机,用于控制8位或16位双向数据总线,并生成多达六个控制(CTL)和九个地址(GPIFADR)输出。

另外,它还接收六个外部和两个内部READY输入,用以确定分支条件。

用户定义的四个波形描述符控制该状态机;8051程序会选择四个波形中的某一个在给定的时间内有效。

每个GPIF波形描述符包含多达七种状态,名称分别为S0-S6。

预定义的S7用于表示闲置状态。

在每个状态内,您可以将GPIF编程为: ▪使某些或所有CTL输出驱动高电平、驱动低电平或悬空▪采样或驱动8/16位数据总线▪递增GPIF地址总线的值▪递增FIFO指针▪向8051触发一个GPIF波形中断 每个状态中的分支决策是通过下列选项得到的两个信号的逻辑AND、OR或XOR: ▪六个READY输入引脚▪内部FIFO标志▪内部RDY标志▪内部事务处理终止标志 通过两个已选信号的逻辑结合可确定下一个状态。

另外,计算好可编程延迟后,状态机会转入下一个状态。

该延迟的范围为1到256个时钟周期。

采样和分支的状态被称为“决策点”。

不带决策点的所有状态仅会维持一个时钟间隔,在下一个时钟间隔内,它将自动转到下一个状态。

文档编号.001-92462版本.*

A 3 图

5.GPIF状态机句法A(func)BisFALSE EZ-USB®FX2LP™GPIF入门 _TRIGCPU IDLE State7 NonDecision Point DecisionPoint State0 State1 A(func)BisTRUE (func)=AND,OR,XOR 3.2 3.2.1 3.2.23.2.33.2.43.2.53.2.6 图5中的状态机的流程如下所示:

1.从闲置状态开始,等待CPU_TRIG信号激活。

2.激活CPU_TRIG时,转入状态0;在该状态中,您可以激活某些控制信号输出,移动数据或递增地址总线。

该状态仅在下一个时钟前持续,因为没有任何决策,所以下面它会无条件地转入状态

1。

3.并保持状态

1,直到两个信号A和B的逻辑组合为真为止(即它为错误时)。

例如,要想一直保持状态

1,直到READY信号有效或完成一个计数为止,那么需要选择A代表READY输入,并选择B代表一个计数器到期。

如果发生两个条件其中一个(READY或终端计数),状态机可通过使用逻辑运算符OR输出状态

1。

4.当该条件为真时,将转入闲置状态。

状态机也随即停止。

物理互连 GPIF互连包含一个8位或16位的数据总线、地址总线、控制输出和就绪输入(图4)。

另外它还包含了三个GSTATE输出(用于指出GPIF机械的当前状态),用于调试目的。

本节详细说明了这些信号。

IFCLKIFCLK(接口时钟)是所有GPIF操作的参考时钟。

可将其作为输入或输出信号使用;并且您可以将上升沿或下降沿选为有效沿。

当作为输入信号使用时,可以使用一个频率为5MHz到48MHz的外部时钟驱动它。

作为输出信号使用时,可以使用FX2LP中一个频率为30MHz或48MHz的内部时钟进行驱动IFCLK。

如果外部外设需要的时钟频率更低,那么可以使用FX2LP的内部时钟切换各CTL线中的某一个。

在第一个示例中,GPIF时钟被2分频和4分频,并通过使用两个CTL输出可以输出这些信号。

如果需要进行更高的分频,请在进入下一个状态前,通过编程GPIF状态计算已编程的时钟数量(1到256)。

GPIFADR[8:0](仅输出)GPIF通过驱动GPIFADR[8:0]为需要地址行的外设提供地址行。

在所有GPIF状态下,可以保持或递增这些输出。

FD[15:0](双向)该数据总线是一个通道,通过它可以在FX2LP端点FIFO和外部外设间传输负载数据。

该信号经配置后可作为8位或16位接口运行。

系统需要时,可进入三态。

在16位模式下,FD[7:0]代表端点FIFO的第一个字节,而FD[15:8]则代表第二个字节。

CTL[5:0](仅输出)控制输出信号可提供外部外设所需要的各种信号,如读/写选通、使能和分频时钟。

RDY[5:0](仅输入)就绪输入信号提供了外部外设的状态信息,如FIFO状态标志和有效数据。

GPIF能将这些信号作为决策点限定符使用。

GSTATE[2:0](仅输出)调试输出信号代表在GPIF波形中执行的状态。

这些信号与逻辑分析仪相连,以用于调试目的。

文档编号.001-92462版本.*

A 4 EZ-USB®FX2LP™GPIF入门 4创建一个GPIF应用 本节介绍了创建GPIF应用的各步骤。

4.1设计GPIF接口 要设计GPIF互连,您需要了解FX2LP和外部外设器件之间的接口。

通过使用FX2LP数据手册和技术参考手册可以定义该接口。

ThefollowingdecisionsdeterminehowtoconfiguretheGPIF. ▪8位或16位数据路径? 该决定通常取决于外设提供的数据路径的大小。

如果大小为16位,则可以使用该路径尽可能扩大物理接口的带宽。

对于16位的数据路径,当连接至数据总线时,需要考虑字节顺序(字节次序)和位编号。

▪外部还是内部接口时钟? 决定取决于外设操作模式的灵活度。

例如,如果它可以接收一个频率为30或48MHz的外部时钟输入,那么内部GPIF时钟便能与外设时钟输入相连。

▪是否需要地址行? 如果在读/写周期操作期间,外设要求对任何寄存器或存储器位置进行寻址,则可以使用GPIFADR[8:0]。

▪控制行 从CTL[5:0]指定GPIF控制输出。

在这些操作中,外设可能需要读/写信号、芯片选择和其他控制输入。

确定有哪些输入,并合理分配CTL[5:0]。

通过GPIFDesigner工具,您能够更清晰地命名这些信号;例如CTL[0]的WR#和CTL[1]的RD#。

▪状态(RDY)行 确定在读/写周期期间需要监控的状态信号数量。

指定包括哪些状态信号,并合适分配RDY[5:0]。

GPIFDesigner工具会再次允许您命名这些信号,以便使这些名称符合您的设计。

▪接口时序 分配输入和输出之后,GPIF应用的主要任务是设计时序波形,从而考虑接口时序。

注意:并非所有FX2LP封装类型均提供GPIF接口信号的完整集。

例如,100引脚和128引脚的FX2LP封装提供了所有六个就绪输入(RDY[5:0])和控制输出(CTL[5:0])。

56引脚封装提供了两个RDY信号RDY[1:0]和三个CTL信号CTL[2:0]。

4.2使用固件框架 使用GPIFDesigner创建接口信号和波形时,您需要使用Keil集成开发环境(IDE)对控制固件进行编写。

开始操作新的FX2LP固件项目时,优先使用基于赛普拉斯编写的固件框架的KeiluVision2项目。

FX2LPDevelopmentKit(DVK)所提供的固件示例都是基于框架的。

您可以使用这些示例其中的任何一个进行操作,或将Keil项目复制到新的子目录内,以进行修改。

这样,您便能够对空的固件基础进行操作。

如果使用了固件框架项目,那么您可以集中到您的应用代码,因为已经写入了USB低电平协议代码。

更多有关信息,请参考fw.c文件和开发套件文档。

应用方案拥有两个主要组件: ▪配置GPIF和启动GPIF传输的固件。

该固件还会执行其他应用任务,如USB枚举和端点配置。

▪实现物理总线时序和数据流的GPIF波形描述符。

该固件包含五个文件:fw.c、periph.c(可以重新命名该文件)、dscr.a51、ezusb.lib和usbjmptb.obj。

这些文件拥有KeiluVision2固件框架项目。

第二个组件是一个包含了代码的C源文件(例如,gpif.c),它用于定义GPIF波形和初始化GPIF单元。

当您通过图形方式定义接口后,GPIFDesigner工具将创建该C文件。

这样便不用知道GPIF单元中的单独寄存器和位。

您可以在此处下载GPIFDesigner工具。

文档编号.001-92462版本.*

A 5 EZ-USB®FX2LP™GPIF入门 4.3使用GPIFDesigner实现GPIF波形 GPIFDesigner生成包含了GPIF波形描述符的C代码,使用这些描述符可以实现接口的物理总线时序。

GPIFDesigner可实现多个波形性能,包括四种波形类型:单写、单读、FIFO写和FIFO读。

CPU通过写入GPIFWFSELECT寄存器控制所使用的波形。

每一个描述符的长度均为32个字节,它位于片上存储器空间内专用的GPIF波形描述区域内。

通过GPIFDesigner工具,您可以将这些描述符作为“黑箱子”使用。

这是因为它可以生成所有需要的C代码,用于实现和使用这些描述符。

将这些GPIF波形作为状态机使用。

存在七种状态或间隔(S0-S6),以及一个用于终止操作的自动闲置状态S7。

图

6.由各状态构成的GPIF波形 将这些GPIF波形作为状态机使用。

存在七种状态或间隔(S0-S6),以及一个用于终止操作的自动闲置状态S7。

图6显示的是一个示例,它说明了一个简单的波形被分解为各GPIF状态转换。

5示例1:对GPIF时钟进行2分频和4分频 首先,需要设计一个状态机用于对GPIF时钟进行2分频和4分频,然后在CTL[0]和CTL[1]上分别输出分频后的时钟信号。

这样,在介绍高级特性包括USB端点FIFO前,可以了解GPIFDesigner工具的基本知识。

由于在本示例中没有使用USB,因此不需要固件框架。

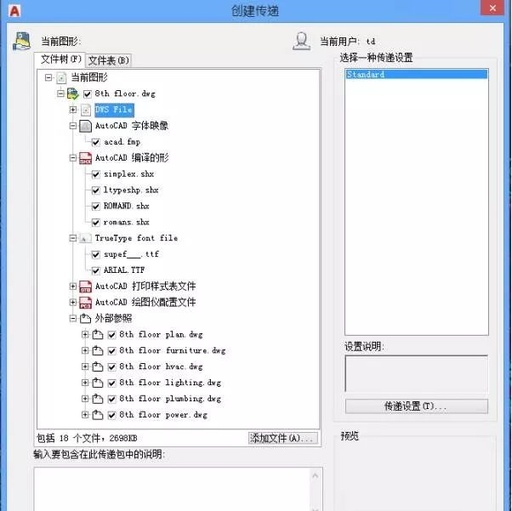

1.解压并存储随本应用笔记附带的FX2LPsourcecodeandGPIFprojectfiles.zip文件。

转到FX2LPSource codeandGPIFprojectfiles\Firmware\GPIFClockDivider。

右击该文件夹并单击Properties(属性)项。

如果选择了“Read-only...”项,请取消勾选它。

点击OK,以允许子目录采用修改内容。

在该文件夹内,双击GPIF_Clock_Divider.uv2。

它包含一个基本的GPIF项目,此项目包含所有信息,但不包括GPIF信息。

双击main.c文件以打开它;您将看到仅需要三行代码便能够启动GPIF操作: WORDg_data;GpifInit();XGPIFSGLDATLX=g_data;//Starttransfer 文档编号.001-92462版本.*

A 6 图

7.基本的GPIFKeil项目 EZ-USB®FX2LP™GPIF入门 如果您没有修改任何代码,您会看到链接器错误,这是因为GPIFKeil项目未包含GPIFDesigner生成的GPIFC文件。

该文件包含GpifInit()函数和波形表数据。

下一步骤将创建该文件。

2.启动GPIFDesigner,然后依次选择File>New打开下面图片显示的窗口。

图

8.GPIFDesigner启动窗口

3.要想使用FX2LP开发板检测该示例,请选择CYFX2(128引脚)并点击OK。

这样可打开框图窗口: 文档编号.001-92462版本.*

A 7 图

9.GPIFDesigner框图 EZ-USB®FX2LP™GPIF入门

4.该框图顶部,右击Clk48MHz文本框配置GPIF时钟。

对于该项目,则保持默认设置。

图10.IFCLK默认设置

5.右击ADR(地址)标签。

该示例没有使用地址总线,因此您可以点击DisableAll;这样会使框图内的各地址行变暗。

文档编号.001-92462版本.*

A 8 图11.禁用地址行 EZ-USB®FX2LP™GPIF入门

6.通过右击RDY(就绪)标签配置六个RDY输入。

该示例没有使用RDY输入,因此未选中这些输入。

要取消选择RDY5,请先取消选择SubstTCforRDY5. 图12.禁用RDY输入

7.通过右击CTL(控制)标签进行配置六个CTL输出。

按照下图设置这些输入。

文档编号.001-92462版本.*

A 9 图13.CTL输出设置 EZ-USB®FX2LP™GPIF入门 将两个输出重新命名为divby2和divby4,并将这两个名称输入到文本框内。

推荐命名您的信号,这是因为它们会更新所有GPIFDesigner屏幕中的标签,从而更容易识别这些信号(例如,divby4而不是CTL1)。

现在该框图会显得更加简单。

图14.时钟分频器框图

8.选择SingleWrite选项卡,以进行绘制两个波形。

右击该选项卡的名称,选择SelectTabLabel,并将其重新命名为Divider。

您会看到一个空白波形的编辑界面,如图15所示。

文档编号.001-92462版本.*

A 10 图15.空白波形编辑器界面 EZ-USB®FX2LP™GPIF入门

9.该状态机有一个名称为IDLE(闲置)的状态。

要想添加某个状态,需要点击CTL带(divby2和divby4)中的某一个。

另外,您还可以通过点击数据带添加各种状态,但该设计不使用数据总线。

在divby2带中,点击第二个垂直虚线。

图16.第一个波形切换 出现的三角形表示GPIFDesigner已经添加了状态s0,并在其开始和结束时切换了divby2输出。

10.现在,请在后面每三个时钟切换虚线上点击divby2波形,这样可创建2分频时钟。

文档编号.001-92462版本.*

A 11 11.在divby4波形中,点击第二个和第四个时钟线。

您的屏幕将显示图17.图17.2分频和4分频波形 EZ-USB®FX2LP™GPIF入门 注意:可通过右击任何一个三角形来修改它的逻辑状态,从而修改信号属性。

另外,通过横向拖动这些三角形,以使某个状态持续时间大于一个时钟。

图17中显示的状态机启动时,它将在每个时钟上升沿上从s0状态依次转到s1、s2和s3,然后以闲置状态停止。

您需要重复该过程;也就是说s3始终要返回到s0状态。

为此,在状态线中将添加一个‘决策点’。

图18.第一个决策点 文档编号.001-92462版本.*

A 12 EZ-USB®FX2LP™GPIF入门 12.点击s2和s3状态之间的状态区间。

这样可添加一个作为决策点的菱形,并显示一个窗口用于配置该决策。

要想进行一个无条件反转,您可以从下拉列表顶部选取两个逻辑信号以及它们的逻辑运算符。

您需要指定THEN和ELSE条件,以切换到S0状态。

也就是要无条件反转到S0状态。

每次进入该状态,可以使用LOOP(Re-Execute)复选框重新激活状态条件。

s3状态中不存在“保持该状态直到发生变化”循环,因此可以取消勾选该项。

在状态s3中,时钟波形显示一个对角线以表示未知决策状态的时钟数量。

这是因为时钟数量取决于满足转换条件的时间。

追踪该设计使用的所有参数,并进行相应的选择项更新。

例如,如果您添加了一个状态s4,那么它将自动被添加到GOTO选项内。

注意:决策点位于状态的开始位置,而不是结束处(决策点在该状态下发生)。

因此,菱形位于s3开始的位置。

13.要存储GPIFDesigner项目,请依次选择File>SaveAs并将该项目存储在Keil项目文件夹asDiv_2_4.gpf内。

如果您想修改当前波形,你可以重新打开该文件。

要存储GPIFDesigner生成的C代码,请依次选择Tools>ExporttoGPIF.cfile并将该代码存储在Keil项目文件夹GPIF_div_2_4.c内。

Div_2_4.gpf和GPIF_div_2_4.c同样也在FX2LPSourcecodeandGPIFprojectfiles\GPIFClockDivider\GPIF_div_2_4文件夹内提供。

通过使用这些文件,您可以直接测试该项目。

14.最后一步是将GPIFDesignerC文件添加到Keil项目。

右击SourcesGroup1并选择Addfiles….找到Keil项目文件夹并添加GPIF_div_2_4.c文件。

图19.将GPIFDesignerC文件添加到Keil项目 15.编译该项目。

KeilIDE编译并链接这些文件,然后通过调用‘hex2bix’工具将负载模块转换为一个与赛普拉斯USB控制面板加载程序相兼容的格式。

按照下列步骤进行操作,您可以在FX2LP开发板上尝试执行该设计:

1.关闭EEPROMSELECT开关。

以使能FX2LP片上的USB代码加载程序。

文档编号.001-92462版本.*

A 13 EZ-USB®FX2LP™GPIF入门

2.将FX2LP板插入到PCUSB端口。

如果是第一次操作,您会看到弹出消息,提示您安装USB驱动程序。

请找到C:\Cypress\USB\CY3684_EZ-USB_FX2LP_DVK\1.0\Drivers\cyusbfx1_fx2lp,然后选择对应WindowsOS的文件夹。

您可以通过查看WindowsDeviceManager(Windows器件管理程序)来确认驱动程序是否安装成功: 图20.赛普拉斯USB加载驱动程序已安装

3.在C:\Cypress\CypressSuiteUSB3.4.7\CyUSB.NET\bin\CyControl.exe中启动USB控制面板。

4.在左侧面板上,您可看到FX2LP板以及与其相连的其他USB器件。

如果仅需查看FX2LP板,则在右侧面板上点击DeviceClassSelection选项卡,并取消勾选除DevicesservedbytheCyUSB.sysdriver(oraderivative)外的所有选项。

左侧面板如图21所示。

图21.USB控制中心内的FX2LP板

5.现在您可以将Keil编译的十六进制文件加载到该板上。

加亮显示EZ-USB输入并选择ProgramFX2>RAM. 文档编号.001-92462版本.*

A 14 图22.将新器件代码加载到RAM EZ-USB®FX2LP™GPIF入门

6.按下FX2LP开发板上的RESET按键,以使能USB加载程序。

7.找到Keil项目文件夹并选择Keil编译器的结果GPIF_Clock_Divider_Proj.hex.8.用探针检测P2引脚11(CTL0=divby2)和P2引脚10(CTL1=divby4)。

此时,您可以看到如图23所示的 波形。

图23.进行2分频和4分频后的GPIF48MHz时钟 文档编号.001-92462版本.*

A 15 EZ-USB®FX2LP™GPIF入门 6示例2:对GPIF时钟进行7分频 通过修改示例

1,您可以选择任何时钟分频器,即使使用的是奇数除数的时钟。

1.启动GPIFDesigner;依次选择File>New来创建GPIF项目。

选择CYFX2(128pin)器件。

2.清除先前描述的ADR和RDY信号,并将CTL0重新命名为divby7,然后将CTL1重新命名为stb。

禁用其他四个 信号。

图24.两个输出:7分频和探针

3.选择SingleWrite选项卡。

在divby7带中,在第一个三角形后面的三个时钟位置上放置一个状态转换三角形,并在其后面四个时钟所在的位置上放置另一个三角形。

在离stb带开始后一个时钟的位置上放置一个三角形;右击第一个三角形,并将它设置为HI;将第二个三角形设置为LO。

这样会将负极性脉冲转换为状态s0中的正极性脉冲。

这时,波形如图25所示。

图25.7分频和探针波形

4.最后,点击时钟线上的状态带,该线同状态s2结束前面一个时钟的位置相对应。

这样可以创建决策点和新状态s3。

应该将该决策点配置为无条件转换到状态S0。

由于THEN和ELSEGOTO的状态都是S0,因此IF条件不重要——您可以从下拉列表中选择任何IF条件。

文档编号.001-92462版本.*

A 16 图26.无条件转换到S0 EZ-USB®FX2LP™GPIF入门 图27.进行7分频的最后波形

5.将该文件(Tools>ExporttoGPIF.c)导出到Keil项目文件夹内,并将它命名为GPIF_div_7.c。

将该项目文件(File>SaveAs)保存为Div_by_7.gpf。

Div_by_4.gpf和GPIF_div_7.c文件也在FX2LPSourcecodeandGPIFprojectfiles\GPIFClockDivider\GPIF_div_7文件件中提供。

您可以直接使用这些文件,进行该项目的测试。

6.在KeilFiles选项卡中,右击SourceGroup1,点击AddFiles…并将GPIF_div_7.c添加到该项目内。

现在您拥有两个GPIF波形文件,因此Keil编译器需要确定将要使用的文件。

要想禁用编译中的任何源文件,需要右击它,选择Optionsforfile…,并取消勾选IncludeinTargetBuild复选框。

如果您的项目中拥有多个GPIF.c文件,请确保仅勾选其中一项。

7.选择Project>RebuildAllTargetFiles,进行重新编译。

8.按下FX2LP开发板上的RESET,这样可以恢复USB代码加载程序的状态。

9.使用USB控制中心面板加载新编译的GPIF_Clock_Divider_Proj.hex文件。

10.探针P2引脚11(CTL0=divby7);您的屏幕将如图28所示。

文档编号.001-92462版本.*

A 17 EZ-USB®FX2LP™GPIF入门图28.顶部:7分频;底部:stb信号的宽度为一个时钟,以用于参照目的 如果您需要更长的时钟分频(如87分频),将如何进行?GPIFDesigner允许您设置一个状态的持续时间为1到256个时钟。

点击状态带中的任何状态;将出现如图29中所示的窗口。

点击SetStateDuration,然后设置时钟数量(图30)。

当您对某个状态的时钟数量进行手动设置时,时序框图的时钟线将不再指出该状态的时钟数。

图29.s2状态的属性 图30.选择1到256个时钟周期 7示例3:使用单个字的读/写数据操作 在该示例中,FX2LP数据通过赛普拉斯CY7C4265-15AXC外部FIFO进行循环。

该示例使用GPIF手动模式并通过一个16位数据总线进行单次的读/写GPIF数据操作。

您可以使用示波器或逻辑分析仪监控FIFO写操作,但在检测读操作时,您需要将外部FIFO芯片连接至FX2LP开发板。

例如,使用开发套件所提供的原型电路板将外部FIFO安装到FX2LP开发板上。

如需了解外部FIFO的全部硬件规范,请下载CY7C4265数据手册。

通过单次读/写操作可在FX2LP和外设之间传输一个字节/字的数据。

与FIFO读/写操作相比,这些操作更简单,因此应该优先执行这些操作。

如果在GPIF开发周期中您先执行该步骤,那么在处理更复杂的设计前,您需要验证系统的所有部分(硬件、固件、软件)。

在验证完物理互联和基本数据传输后,应该转到完整的设计。

文档编号.001-92462版本.*

A 18 EZ-USB®FX2LP™GPIF入门 7.1.17.1.2 执行FIFO读/写操作执行完单次操作后,需要执行GPIFFIFO读/写操作,以增大带宽。

先实现FIFO写波形可避免检测整个环回方案时遇到问题;如果它不工作,那么很难区分该问题是读操作、写操作还是两个操作。

需要时进行优化生成GPIF波形时,要先设置物理总线为高电平的时间。

这样可以缩短每个GPIF操作的循环时间,同时仍可满足外设所要求的时序参数。

您还可以对该设计进行修正,以提高固件代码的效率,并改进本阶段的整体固件代码流。

图31通过使用GPIF设计流程图对本章进行了总结。

图31.GPIF设计流程图 DesignGPIFInterconnect UseFirmwareFrameworks 8-or16-bit?

InternalorExternalIFCLK?

No.ofGPIFADR[8:0] Lines?

No.ofCTL[5:0]Lines?

No.ofRDY[5:0] Lines?

OtherI/OLines?

ImplementGPIFWaveformDescriptors ImplementSingleRead/WriteTransactions IntegrateandTest No CompletedatapathverifiedandPhysicalinterconnectfleshedout?

Yes NoImplementFIFORead/WriteTransactions IntegrateandTest Completedatapathverified?

Yes OptimizeifNecessary 文档编号.001-92462版本.*

A 19 EZ-USB®FX2LP™GPIF入门 7.1.3 将FIFO连接至FX2LPGPIF接口显示的是FX2LP与外部FIFO之间的连接。

FX2LP使用其双向总线FD[15:0]对外部FIFO中的数据进行读写。

通过将FIFO的输出数据总线Q[15:0]和输入数据总线D[15:0]连接在一起,可将FIFO数据总线设置为双向。

该示例通过USBBULK传输对FIFO数据进行读写。

使用SuiteUSB3.4-USBDevelopmenttoolsforVisualStudio所提供的USB控制中心,可以执行这些传输。

表1对GPIF互联进行了详细说明。

指定CTL和RDY引脚与最小FX2LP封装(包含56个引脚)相兼容。

图32.GPIF与外部同步FIFO间的连接 FX2LPIFCLK CY7C4265-15ACRCLKWCLK FD[15:0] DATA[15:0]D[15:0] CTL0CTL1CTL2 RDY0RDY1 PA2 DATA[15:0]Q[15:0] WEN#REN#OE# EF#FF# RS# FX2LPGPIF信号IFCLK FD[15:0] CTL0CTL1CTL2 CY7C426515AXC信号WCLK,RCLK D[15:0],Q[15:0] WEN#REN#OE# 表

1.分配至CY7C4265-15AC信号的FX2LPGPIF信号 说明 IFCLK连接到外部FIFO的读写时钟输入(WCLK、RCLK)。

确认WEN#时,数据在每个WCLK上升沿上为外部FIFO提供时钟脉冲。

同样,确认REN#和OE#时,FIFO在RCLK每个上升沿上的Q[15:0]显示数据。

外部FIFO可接受最大为66.7MHz的输入时钟频率,因此,能够处理的输入IFCLK频率为30MHz或48MHz。

请注意井字符(例如OE#)表示低电平有效。

GPIF数据总线(FD[15:0])连接至外部FIFO的输入数据总线(D[15:0]),以进行字操作。

外部FIFO的输出数据总线Q[15:0]也被连接至GPIF数据总线,以便FX2LP可以读回数据内容。

由于两个单向FIFO数据总线彼此连接,因此GPIF必须控制OE#信号,以避免发生总线冲突。

特别是当FX2LP驱动数据总线时,不能将OE#置于低电平状态—这是因为FX2LP和FIFO同时驱动数据总线时,会导致总线冲突。

CTL0连接至外部FIFO写使能引脚WEN#。

GPIF将WEN#置于低电平时,在每个WCLK上升沿上将数据写入到外部FIFO内。

CTL1连接至外部FIFO读使能引脚REN#。

当GPIF将REN#和OE#置于低电平时,FIFO在RCLK的每个上升沿上驱动Q[15:0]中的数据。

CTL2连接至外部FIFO输出使能引脚OE#。

将REN#和OE#置于低电平时,FIFO在RCLK的每个上升沿上驱动Q[15:0]上的数据。

文档编号.001-92462版本.*

A 20 EZ-USB®FX2LP™GPIF入门 FX2LPGPIF信号 RDY0 CY7C426515AXC信号 EF# RDY1 FF# PA2 RS# 说明 RDY0连接至外部FIFOEMPTY标志EF#,如果FIFO为空,它将置于低电平。

由于能够在GPIF转换状态中检测READY信号,因此从外部FIFO读取数据时,GPIF可以使用该信号进行控制数据传输。

RDY1连接至外部FIFOFULL标志FF#,如果FIFO已满,它将置于低电平。

当写入外部FIFO时,GPIF可使用该信号控制数据传输。

PA2连接到外部FIFORESET引脚。

PA2是一个FX2LPGPIO引脚,并且不属于GPIF逻辑。

在启动GPIF数据传输前,8051代码会使用PA2将外部FIFO复位到一个已知状态。

8USB数据流 USB端点2OUT(EP2OUT)作为GPIF写入外部FIFO的发送端点使用,端点6IN(EP6IN)作为GPIT从外部FIFO读取的接收端点使用。

从主机端的角度来看,USBIN和OUT方向如下: ▪EP2OUT包含了USB主机(PC)发送和FX2LP接收的数据包。

▪EP6IN包含了FX2LP发送和PC接收的数据包。

9设计GPIF互联 通过使用第一个示例中所描述的GPIF各步骤可以设置GPIF互联,具体如下。

1.启动赛普拉斯GPIFDesigner工具。

2.请依次选择File>New,然后选择FX2LP开发板使用的CYFX2(128pin)。

3.右击外部器件模块中的Un-named标签并将其重新命名为CY7C4265-15AC.4.默认情况下,数据总线被配置为16位。

该示例使用了16位数据总线。

5.右击ADR标签。

该设计没有使用地址行,因此可禁用它们以简化框图。

6.右击RDY标签,并对RDY信号进行配置,如图33中所示。

图33.RDY引脚配置

7.右击CTL标签,并对CTL信号进行配置,如图34所示。

文档编号.001-92462版本.*

A 21 图34.CTL引脚配置 EZ-USB®FX2LP™GPIF入门 .8.右击48MHzCLK文本框,并按照图35的内容配置时钟属性。

选择InvertClock复选框。

GPIF更改并采样时钟 上升沿上的信号;FIFO将更改并采样时钟下降沿上的信号。

这个半时钟偏移提供了各种接口时序设置和保持时间。

图35.配置IFCLK 该框图将如图36所示。

现在,该时钟被标签为“nClk48Mhz”,其中“n”表示时钟反转。

图36.FIFO的配置接口 文档编号.001-92462版本.*

A 22 EZ-USB®FX2LP™GPIF入门 9.1单字写波形 通过写波形,可以将数据从FX2LPOUT端点FIFO传输到外部FIFO。

右击FIFORead选项卡并将其重新命名为“Unused”。

对FIFOWrite选项卡进行类似操作。

您的屏幕将如图37所示。

图37.波形屏幕 请依次点击Tools>MapWaveforms进行WFSELECT(选择波形)(图38)。

图38.波形映射对话框 请确保单写波形被映射到SINGLEWR,而单读波形被映射到SINGLERD。

这样可对8051寄存器进行配对(这些寄存器将这些波形设置为GPIF命名的波形)。

注意:波形映射允许您为同一类传输定义多个波形组。

例如,您可以将两种不同的波形类型使用在单写操作中。

通过写波形可以管理各字节传输,这些字节传输将FX2LPOUT端点的数据传输到外部FIFO。

要想创建FIFO写波形,请先检查CY7C4265数据手册中提供的CY7C4265FIFO的写周期时序。

图39显示的是写周期时序,其中GPIF状态被添加到该框图的底部。

文档编号.001-92462版本.*

A 23 图39.写周期时序框图 EZ-USB®FX2LP™GPIF入门 IDLE S0 S1 在写周期时序框图中,您可以创建如图40.图40.单字FIFO写状态框图 S0 WEN#=0REN#=1OE#=1Activate Data S1 WEN#=1REN#=1OE#=1Deactivate Data Initiate S7(IDLE) WEN#=1REN#=1OE#=1Deactivate Data ▪对于单写波形,通过将WEN#逻辑置于低电平和驱动数据总线,可以在状态S0期间将数据写入到外部FIFO内。

文档编号.001-92462版本.*

A 24 EZ-USB®FX2LP™GPIF入门 ▪在状态S1内,WEN#被禁用(为高电平),并且GPIF数据总线停止驱动(悬空)。

S1是一个决策点状态,它会强制无条件转换到闲置状态,从而停止波形。

闲置状态下并没发生任何活动 ▪每次触发单写波形时,GPIF引擎都会经过S0、S1,然后停止于S7(空闲)。

请按照下列各步骤完成单写波形。

1.点击SingleWrite波形选项卡。

2.点击离左边界一个时钟周期的WEN#跟踪,在此处放置一个操作点并创建WEN#波形。

自动生成状态0(s0), 并会持续一个IFCLK周期(20.83ns)。

3.由于GPIF被写入到外部FIFO,因此在波形期间,必须将REN#和OE#置于高电平,为防止外部FIFO驱动它的 数据总线。

为此,需要右击OE#和REN#跟踪上的操作点,并选择High

(1)。

各波形如图41所示。

图41.WEN#在一个时钟内保持低脉冲

4.必须将数据总线驱动到s0状态。

因此,需要右击数据操作点,并选择ActivateData. 应该只在一个时钟周期内驱动数据总线。

经过一个时钟周期后,要想停止驱动数据,需要在数据带中距离第一个时钟一个时钟的位置上放置另一个操作点。

请注意,现在数据带只在s0期间保持为高电平。

各波形如图42中所示。

文档编号.001-92462版本.*

A 25 图42.S0期间,会在一个时钟周期内驱动数据 EZ-USB®FX2LP™GPIF入门

5.通过创建一个决策点状态S1可以返回闲置状态。

在S0状态的右边界上点击状态带,然后按照图43中显示的内容设置无条件转换。

图43.无条件转换到闲置状态 单个字写波形如图44所示。

图44.单子写波形 文档编号.001-92462版本.*

A 26 EZ-USB®FX2LP™GPIF入门 9.2单字读波形 通过读波形可以管理从外部FIFO到FX2LPIN端点将FIFO的字节传输。

类似于写周期,GPIF波形必须满足外部FIFO时序的要求。

首先,需要检查外部FIFO的读周期时序,然后创建单读状态机。

图45显示的是CY7C4265的读周期时序,其中GPIF状态被添加到该框图的底部。

图45.读周期时序框图 S0 S1 S2 通过时序信息您可以创建如图46所示的状态机,以用于字节读操作。

. 图46.字节读状态框图 S0 WEN#=1REN#=0OE#=

1 S1 WEN#=1REN#=1OE#=

0 Initiate S7(IDLE) WEN#=1REN#=1OE#=

1 S2 WEN#=1REN#=1OE#=0ActivateData 文档编号.001-92462版本.*

A IDLE 27 EZ-USB®FX2LP™GPIF入门 ▪对于单读波形,在S0状态期间,REN#在一个IFCLK周期内保持逻辑低电平状态。

这样会在确认OE#前,外部FIFO需要记录在数据手册中的tENS设置时间。

经过一个时钟后取消确认REN#可确保FIFO未递增一个字,以执行读操作。

▪然后S1将确认OE#并转到S2状态。

▪由于它需要进行反转,因此S2作为决策点状态。

S1状态开始阶段,仍无法从外部FIFO获得数据,因此,GPIF 只能在S2开始时“采样”数据。

▪每次触发单读波形时,GPIF引擎都会按S0、S1、S2和S7的顺序循环。

请按照下列各步骤创建单读波形。

1.点击SingleRead波形选项卡。

2.右击REN#跟踪中的第一个时钟,并选择Low

(0)。

点击离左边界一个时钟周期的REN#跟踪,在此放置一个操作 点,并创建REN#脉冲。

自动生成状态0(s0),并会持续一个IFCLK周期(20.83ns)。

因此,REN#在20.83ns时间内有效(图47)。

图47.REN#在一个时钟内有效

3.在OE#带内,将一个操作点放置在S0的右边界上,并在离它后面一个时钟的位置上放置另一个操作点。

这样,在完成状态S0后,可自动取消确认OE#并创建持续一个IFCLK周期的S1(20.83ns)状态。

图48.OE#在一个时钟内有效 文档编号.001-92462版本.*

A 28 EZ-USB®FX2LP™GPIF入门

4.通过点击时钟终端s1上的状态带来添加一个决策点(DP)状态。

从而创建状态S2,并会弹出“SpecifyDecision Point”对话框。

按照图49配置该决策点,为了无条件转换到闲置状态。

这时,您的波形将如图50所示。

图49.无条件转换到闲置状态 图50.添加了状态s2

5.最后需要进行的调整。

必须在S2期间采样(读)数据。

要想采样该数据,需要将操作点放置在S2状态的开始和结束的数据带上。

请注意,由于当前是在SingleRead(单读)选项卡中进行操作,因此高电平对应于采样,而不是驱动数据带。

最后,单个字读波形如图51所示。

6.通常,您应该将GPIFDesigner项目文件(*.gpf)和它生成的C文件存储在您的Keil项目文件夹内。

在这个范例中,它们已经作为本应用笔记的代码显示在该文件夹内。

文档编号.001-92462版本.*

A 29 图51.最后单个字读波形 EZ-USB®FX2LP™GPIF入门 9.3单个字操作的固件编程 在GPIFDesigner中实现单字操作波形后,需要将USB固件与GPIFDesigner输出集成在一起。

这样可以通过USB对外部FIFO进行读写操作。

开始对现有的固件框架项目进行操作并且添加GPIF管理代码。

双击Keil项目文件FX2_to_extsyncFIFO.uv2.该文件打开时,将出现Files(文件)面板,如图52。

表2介绍了这些文件。

图52.“FX2_to_extsyncFIFO”项目文件 已经将periph.c重命名为FX2_to_extsyncFIFO.c。

在该文件内,将USB端点和GPIF初始化代码添加到TD_Init()函数内,并将GPIF管理代码添加到TD_Poll()函数内。

表

2.项目文件说明 文件fw.cEzusb.libUSBJmpTb.OBJDscr.a51FX2_to_extsyncFIFO.c(由periph.c重命名得到)Gpif.c 说明固件框架用于处理USB请求,并调用任务调度程序TD_Poll()。

处理暂停、恢复、I2C等操作的函数集。

USB(INT2)和GPIF/从设备FIFO(INT4)中断源的中断矢量跳转表。

将EP2OUT和EP6IN作为FX2LP器件可用端点报告的FIFO示例器件描述符表。

可在这里找到TD_Poll()和TD_Init()的主用户应用代码。

您需要修改该文件,并不更新fw.c。

包含了执行单/FIFOGPIF操作波形特性的GPIF波形描述符表的文件。

它是从GPIFDesigner工具导出的C文件。

文档编号.001-92462版本.*

A 30 EZ-USB®FX2LP™GPIF入门 9.4 9.4.1 代码段 TD_Init()TD_INIT()进行下列操作: ▪将CPU时钟速度切换到48MHz(加电状态时默认速度为12MHz)▪将EP2配置为批量OUT端点,大小为512缓存的4倍▪将EP6配置为批量IN端点,大小同样为512缓存的4倍▪将FIFO配置为手动模式的字操作▪使用FIFORESET寄存器复位这些端点,并使EP2OUT端点确保可以接收USB主机(PC)中的数据 voidTD_Init(void) // { //settheCPUclockto48MHz CPUCS=((CPUCS&~bmCLKSPD) SYNCDELAY; Calledonceat|bmCLKSPD1); startup EP2CFG=0xA0;SYNCDELAY;EP4CFG=0x00;SYNCDELAY;EP6CFG=0xE0;SYNCDELAY;EP8CFG=0x00;SYNCDELAY; //EP2OUT,bulk,size512,4xbuffered//EP4notvalid//EP6IN,bulk,size512,4xbuffered//EP8notvalid EP2FIFOCFG=0x01;//manualmode,disablePKTENDzerolengthsend,wordops SYNCDELAY;EP6FIFOCFG=0x01;//manualmode,disablePKTENDzerolengthsend,wordopsSYNCDELAY; FIFORESET=SYNCDELAY;FIFORESET=SYNCDELAY;FIFORESET=SYNCDELAY;FIFORESET=SYNCDELAY; 0x80;0x02;0x06;0x00; //setNAKALLbittoNAKalltransfersfromhost//resetEP2FIFO//resetEP6FIFO//clearNAKALLbittoresumenormaloperation //outendpointsdoeuparmed//becauseEP2OUTisquadbuffered,writedummybytecountsfourtimes EP2BCL=0x80;SYNCDELAY;EP2BCL=0x80;SYNCDELAY;EP2BCL=0x80;SYNCDELAY;EP2BCL=0x80; //armEP2OUTbywritingbytecountw/skip. 文档编号.001-92462版本.*

A 31 EZ-USB®FX2LP™GPIF入门 SYNCDELAY; GpifInit();//initializeGPIFregisters ▪然后,TD_Init将调用位于gpif.c中的函数GPIFInit()。

▪GPIFInit()将GPIF波形描述符表加载到片上存储器内,并对其他GPIF寄存器进行配置。

▪每次只能加载四种波形。

如果描述物理接口操作所需的波形超过了四种,则必须手动加载另外一套四种波形。

▪IFCONFIG寄存器通过定义物理接口的GpifInit()函数被配置。

▪TD_Init()通过脉冲PA2(RS#)复位外部FIFO,如下面代码段中所示。

这样可确保在启动数据操作前已经初始化外 部FIFO。

//resettheexternalFIFO OEA|=0x04; //turnonPA2asoutputpin IOA|=0x04; //pullPA2highinitially IOA&=0xFB; //bringPA2low EZUSB_Delay

(1);//keepPA2lowfor~1ms,morethanenoughtime IOA|=0x04; //bringPA2high ▪在下面的代码中定义了USB供应商指令0xB2。

它允许主PC通过发出供应商指令复位外部FIFO。

BOOLDR_VendorCmnd(void){switch(SETUPDAT[1]) {caseVX_B2: {//resettheexternalFIFO OEA|=0x04; //turnonPA2asoutputpin IOA|=0x04; //pullPA2highinitially IOA&=0xFB; //bringPA2low EZUSB_Delay

(1);//keepPA2lowfor~1ms,morethanenoughtime IOA|=0x04; //bringPA2high *EP0BUF=VX_B2;EP0BCH=0;EP0BCL=1;EP0CS|=bmHSNAK; break;} //Armendpointwith#bytestotransfer//Acknowledgehandshakephaseofdevicerequest 文档编号.001-92462版本.*

A 32 EZ-USB®FX2LP™GPIF入门 9.4.2 触发GPIF单个字写操作 ▪8051代码通过访问XGPIFSGLDATH、XGPIFSGLDATLX和XGPIFSGLDATLNOX寄存器触发单个字读/单个字写GPIF波形。

从而启动数据传输。

▪为了触发GPIF单个字写操作,您需通过以下方式写入XGPIFSGLDATH和XGPIFSGLDATLX: XGPIFSGLDATH=>>8;XGPIFSGLDATLX=;transaction

//triggerGPIFSingleWordWrite

▪这样可以将单字值MSB和LSB设置为可传输的,同时,对XGPIFSGLDATLX寄存器进行的写操作可触发单个字写操作。

▪在本示例中,该操作是在GPIF_SingleWordWrite()函数内执行的。

该函数把一个字的值作为输入参数使用,并触发GPIF单字写操作。

voidGPIF_SingleWordWrite(WORDgdata){while(!

(GPIFTRIG&0x80))//pollGPIFTRIG.7Donebit {; } //usingregistersinXDATAspaceXGPIFSGLDATH=gdata;XGPIFSGLDATLX=gdata>>8; Writetransaction} //triggerGPIFSingleWord 9.4.3 ▪该函数在启动操作前通过轮询位GPIFTRIG.7检查GPIF是否处于IDLE(闲置)状态(如果GPIF状态机为闲置状态,将设置该位)。

在启动任何一个GPIF操作前,都必须始终确保GPIF处于闲置状态。

▪请注意单个操作寄存器的访问顺序,因为端点缓冲区是以FIFO形式进行组织的。

这样的顺序可确保端点缓冲区的第一个字节在FD[7:0]被写出,第二个字节在FD[15:8](低位优先格式)被写出。

GPIF单字读操作 ▪通过从XGPIFSGLDATX寄存器执行虚拟读,可以触发GPIF单个字读操作。

该读操作并没有进行任何数据传输,它仅启动了GPIF波形。

检测GPIFDONE位后,8051将读取XGPIFSGLDATH和XGPIFSGLDATLNOX寄存器中的字量。

▪在本示例中,此操作是在GPIF_SingleWordRead()函数内执行的。

该函数把目标变量的字指针作为参数使用,并执行GPIF单字读操作: voidGPIF_SingleWordRead(WORDxdata*gdata) { staticBYTEg_data=0x00; //dummyvariable while(!

(GPIFTRIG&0x80)){;} //pollGPIFTRIG.7Donebit //usingregisterinXDATAspace g_data=XGPIFSGLDATLX; //dummyreadtotriggerGPIF //SingleWordReadtransaction 文档编号.001-92462版本.*

A 33 EZ-USB®FX2LP™GPIF入门 while(!

(GPIFTRIG&0x80)){;} //pollGPIFTRIG.7Donebit 9.4.4 //usingregister(s)inXDATAspace,retrievewordjustreadfromext.FIFO*gdata=((WORD)XGPIFSGLDATLNOX<<8)|(WORD)XGPIFSGLDATH; } ▪该函数会先确保GPIF处于闲置状态,然后才从XGPIFSGLDATLX执行虚拟读,以触发GPIF单字读操作。

然后,在读取包含了字值的寄存器前,它会等待完成GPIF的执行。

TD_Poll() ▪位于函数TD_Poll()内的主应用代码会在器件操作期间被连续调用。

▪在此函数中,要调用GPIF_SingleWordWrite()和GPIF_SingleWordRead()函数。

▪GPIF_SingleWordWrite()将EP2OUT中的数据发送到外部FIFO,而GPIF_SingleWordRead()会读取外部FIFO 中的数据,并将结果写入到EP6IN内。

▪处理USBOUT传输的代码如下: if(!

(EP2468STAT&bmEP2EMPTY)&&(EXTFIFONOTFULL)){ //ifhostsentdatatoEP2OUTANDexternalFIFOisnotfull, Tcount=(EP2BCH<<8)+EP2BCL;//loadtransactioncountwithEP2byte count Tcount/=2; //divideby2forwordwidetransaction Source=(WORD*)(&EP2FIFOBUF); for(i=0x0000;i▪另外,通过访问GPIFREADYSTAT寄存器,可以检查外部FIFO中的FF#标志。

这样可以确保外部FIFO中有足 够的空间用于存储从EP2OUT传输来的数据。

8051通过访问GPIFREADYSTAT寄存器检查GPIFRDY信号的状态。

EXTFIFONOTFULL是GPIFREADYSTAT的宏,它同bmBIT1进行AND运算。

▪如果EP2OUT端点中有数据,并且外部FIFO未满,那么字变量Tcount将使用计数值初始化。

通过访问EP2BCH/L寄存器,可以查看从主机传输到EP2OUT的字节数量。

每个GPIF单字写操作都会将一个字发送至外部FIFO,因此,操作数始终是端点缓冲区实际包含字节数的一半。

▪然后,“Forloop”语句以“Tcount”的次数调用GPIF_SingleWordWrite函数,并索引端点缓冲区EP2值,这样是为每次能以一字的方式向外部FIFO发送数据。

每个循环都会触发一个GPIF单写操作,因此每次将一个字的数据发送到外部FIFO。

▪传输“Tcount”字的数据后,将重新激活EP2端点,以便可以接受主机中的下个USB数据包。

FX2LP会自动否认所有OUT数据包,直到可以接收新的数据包为止。

因此,主机需要连续重试OUT传输。

文档编号.001-92462版本.*

A 34 EZ-USB®FX2LP™GPIF入门 ▪处理USBIN传输的代码如下: if(in_enable)//ifINtransfersareenabled,{ if(!

(EP2468STAT&bmEP6FULL)&&(EXTFIFONOTEMPTY)){ //ifEP6INisnotfullANDthereisdataintheexternal FIFO, Destination=(WORD*)(&EP6FIFOBUF); for(i=0x0000;i

▪如果EP6IN端点缓冲区未满,并且外部FIFO非空,则“forloop”将调用GPIF_SingleWordRead()函数。

从而触发一个GPIF字读取,并将该结果存储在目标地址中(该地址被设置为EP6INFIFO)。

每个重复次数都会递增目标地址,从而将在外部FIFO中检索到的字节填充到EP6INFIFO内。

▪将外部FIFO数据填充到EP6INFIFO后,8051代码会通过使能EP6IN端点将数据传输到主机PC。

使能前,FX2LPUSB逻辑会自动否认EP6的所有主机IN请求。

8051代码通过写入一个字节数(表示主机IN传输的字节数量)使能IN端点。

由于每个GPIF单字读操作接收外部FIFO中包含的两字节的整个字,因此,发送至主机的字节数始终是GPIF操作数的两倍。

▪通过将相应的值分配给“in_enable”标志,可以使能或禁用IN传输。

本示例定义了两条供应商指令,一个使能IN传输,另一个禁用IN传输,如下面代码所示: caseVX_B3://enableINtransfers{in_enable=TRUE;*EP0BUF=VX_B3;EP0BCH=0;EP0BCL=1;EP0CS|=bmHSNAK;break; }caseVX_B4://disableINtransfers{ 文档编号.001-92462版本.*

A 35 EZ-USB®FX2LP™GPIF入门 9.5 9.5.1 in_enable=FALSE;*EP0BUF=VX_B4; EP0BCH=0;EP0BCL=1;EP0CS|=bmHSNAK;break;} ▪IN供应商指令0xB3通过将in_enable设置为TRUE(真)来使能IN传输。

▪IN供应商指令0xB4通过将in_enable设置为FALSE(假)来禁用IN传输。

▪in_enable的默认值为FALSE。

▪通过in_enable标志您可以对每一次读写操作单独进行测试。

如果它始终被使能,那么将立即在OUT传输代码后 处理IN传输代码。

通过单步处理该代码,您可轻松捕获使用逻辑分析仪的每个读/写操作(适用于调试目的)。

运行GPIF单个字操作示例 不存在外部FIFO如果您尚未构建包含外部FIFO的FX2LP开发板,您同样能够使用示波器来观察GPIF写传输。

这样可以验证将数据从PC传输到FX2LP芯片的USB代码,以及将数据输出到外部FIFO的GPIF波形。

1.通过探针FX2LP开发板上的P2-11观察CTL0=WEN#,并且通过探针P1-19观察FIFO数据总线D0。

2.启动USB控制中心。

将FX2LP开发板插入到主PC端口内,该端口应该作为USB加载程序器件(如图21所示) 进行枚举。

否则,按照进入图21的各步骤进行操作。

3.请依次选择ProgramFX2>RAM并找到FX2_to_extsyncFIFO.hex文件以加载它。

4.展开Bulkloop器件并选择Bulkoutendpoint(0x02)。

5.在Datatosend(Hex)文本框内输入图53中显示的数字。

6.点击TransferData-OUT按键。

图53.USB控制中心传输数据

7.右下角中的文本窗口可确认该传输,并且应该在WEN#脉冲的下降沿上触发该示波器(图54). 文档编号.001-92462版本.*

A 36 图54.顶部:WEN#,底部:FD[0] EZ-USB®FX2LP™GPIF入门 9.5.2 9.6 9.6.1 请注意,第一个FIFO写传输会将FD[0]置于高电平,第二个写传输会将FD[0]置于低电平。

这样可以确保16位字按从低到高的顺序输出;第一字为0001,第二字为0100。

存在外部FIFO如果您已经编译好并将外部FIFO添加到开发板上,请先通过传输USB数据OUT测试该环回,如前面所述。

然后,使用同一个字节数进行传输数据IN操作。

本测试使用的是包含512个数据字节的512_count.hex文件。

1.在树状图中选择Bulkoutendpoint(0x02)(批量输出端点(0x02))。

单击DataTransferstab(数据传输)选项卡。

按下TransferFile-OUT按键,并选择Keil项目文件夹:FX2LPSourcecodeandGPIFprojectfiles\Firmware\FX2_to_extsyncFIFOGPIFSingleTransactions中的512_count.hex文件.点击Open,将512个字节发送到外部FIFO。

2.要想使用IN传输从外部FIFO中读回512个字节,必须使用一个USB供应商请求将in_enable标志设置为真。

在树状图中选择Controlendpoint(0x00);在Reqcode字段中输入‘0xB3’。

将ReqType设置为‘Vendor’,将Direction设置为‘In’,并将BytestoTransfer设置为‘1’。

点击TransferData。

3.在树状图中选择Bulkinendpoint(0x86)(批量输入端点(0x86))。

请确保BytestoTransfer中的字节数量为512。

按下TransferData-IN按键。

现在您可以看到从设备FIFO回读的512个字节。

单个字操作的逻辑分析仪波形 本节显示了GPIF引擎为GPIFDesigner定义的波形生成的时序。

单个字写波形 图55.单个字写波形 文档编号.001-92462版本.*

A 37 EZ-USB®FX2LP™GPIF入门 9.6.2 图55显示了GPIF引擎为GPIFDesigner定义的单写波形生成的时序信号。

本文档介绍了所有信号,包括GSTATE[2:0],该信号显示了GPIF引擎循环在执行单写操作时循环所经过的状态。

调试提示: ▪将GSTATE信号突出显示为逻辑分析仪标题时,您可以通过使用物理接口上生成的信号来确认GPIFDesigner波形。

这样还能够为调试流程提供辅助,因为您可以验证状态切换的正确性。

▪S0将数据放置在总线(PORTB为FD[7:0],PORTD为FD[15:8])上,并确认CTL0(连接至外部FIFO的WEN#线)。

该操作可将16位数据值写入到外部FIFO内。

▪请注意,需要为IFCLK上升沿提供足够的数据设置时间,因为外部FIFO的最小设置时间为4ns(请参见CY7C4265数据手册)。

▪S1是一个决策点状态,自动转至闲置状态,以终止该操作。

▪如果不存在无条件转移,那么在达到闲置状态(S7)之前,GPIF引擎将依次经过其余的所有状态(S2-S6)。

▪对于在批量OUT传输中写出的每个字,您应看到GPIF引擎按S0、S1和S7的顺序循环。

▪为捕获波形,请触发位于CTL0下降沿的逻辑分析仪。

▪4ns的采样频率将为您提供与图55所示波形的分辨率。

单个字读波形 图56.单个字读波形 图56显示的是GPIF引擎为GPIFDesigner定义的单个字读波形生成的时序。

本文档介绍了所有信号,其中包括了GSTATE[2:0],该信号显示了GPIF引擎循环在执行单读操作时循环所经过的状态。

调试提示: ▪S0确认CTL1(连接至外部FIFO的REN#线),S1确认CTL2(连接至外部FIFO的OE#线),S2对数据总线进行采样(PORTB为FD[7:0],PORTD为FD[15:8])。

该操作可将16位数据值写入到外部FIFO内。

▪请注意,需要为IFCLK上升沿提供足够的数据设置时间,因为GPIF的最小设置时间为9.2ns(请参见FX2LP数据手册)。

▪S2是一个决策点状态,自动转至闲置状态,以终止该操作。

▪如果没有无条件转移,达到闲置状态(S7)之前,GPIF引擎将依次经过其余所有状态(S3-S6)。

▪对于从批量IN传输中的外部FIFO读取的每个字,您都应看到GPIF引擎按S0、S1、S2和S7的顺序循环。

文档编号.001-92462版本.*

A 38 EZ-USB®FX2LP™GPIF入门 10 10.1 10.210.3 11 ▪为捕获波形,请触发位于CTL1下降沿的逻辑分析仪▪4ns的采样频率将为您提供与图56中的波形显示一样的分辨率。

相关文档 ▪FX2LP™入门:该文档可帮助新用户熟悉FX2LP。

▪FX2LP技术参考手册:本文档作为FX2LP的技术指南使用。

“通用可编程接口(GPIF)”章节对GPIF进行了详 细说明。

▪GPIFDesigner工具用户指南:为打开该文件,需要下载GPIFDesigner中的工具。

安装后,请依次选择Help>ThisTool. ▪EZ-USBFX1-EZ-USBFX2LPDevelopmentKitQuickStartGuide.pdf(EZ-USBFX1-EZ-USBFX2LP开发套件快速入门指南)和EZ-USBDevelopmentKitUserGuide.pdf(EZ-USB开发套件用户指南):这两个文档介绍的都是如何使用CY3684套件,(安装DVK后)C:\Cypress\USB\CY3684_EZUSB_FX2LP_DVK\1.0\Documentation中找到。

▪EZ-USBFX1/FX2LP的端点架构:通过本应用笔记可以了解FX1/FX2LP中的数据流。

其他GPIF示例 可以在下面各赛普拉斯应用笔记中查找更多GPIF示例: ▪AN57322:通过GPIF将SRAM连接至FX2LP:该应用笔记介绍的是如何使用一个GPIF8位异步(无时钟)接口将CY7C1399BSRAM连接至FX2LP。

它还介绍了将FX2LP连接至其它SRAM的指导信息。

▪AN63787:使用8位异步接口的EZ-USBFX2LPGPIF和从设备FIFO配置示例:本应用笔记描述了如何在手动模式和自动模式下配置EZ-USBFX2LP中的通用可编程接口(GPIF)和从设备FIFO,以执行8位异步并行接口。

通过使用两个互联的FX2LP开发板(一个作为GPIF主设备使用,另一个作为GPIF从设备使用)可以测试该设计。

▪AN4051:UDMA的FX2LPGPIF流状态特性:该应用笔记介绍了GPIF的“流状态”特性。

该特性扩展了GPIF的性能,以处理ATAPIUDMA。

参考设计 ▪CY4611B—USB2.0USB到ATA参考设计:流行的FX2LP应用就是USB批量存储器。

通过FX2LPGPIF可以轻松连接至附加驱动。

赛普拉斯提供了一个使用FX2LP的完整批量存储器参考设计。

数据手册 ▪EZ-USBFX2LPUSB微控制器高速USB外设控制器▪CY7C4265数据手册 总结 本应用笔记是用于介绍EZ-USBFX2LPGPIF的文档。

它说明了创建一个通用的可编程接口的操作步骤,并提供了用于描述GPIFDesigner主要特性的各种示例。

文档编号.001-92462版本.*

A 39 EZ-USB®FX2LP™GPIF入门 文档修订记录 文档标题:AN66806-EZ-USB®FX2LP™GPIF入门文档编号:001-92462 修订版***

A ECN43768685880686 原始变更LISZSXFS 提交日期08/29/201409/12/2017 变更说明本文档版本号为Rev**,译自英文版001-66806Rev*

D。

本文档版本号为Rev*

A,译自英文版001-66806Rev*

G. 文档编号.001-92462版本.*

A 40 EZ-USB®FX2LP™GPIF入门 全球销售和设计支持 赛普拉斯公司拥有一个由办事处、解决方案中心、厂商代表和经销商组成的全球性网络。

要找到离您最近的办事处,请访问赛普拉斯所在地。

产品 ARM®Cortex®微控制器汽车级产品时钟与缓冲器接口物联网存储器微控制器PSoC电源管理IC触摸感应USB控制器无线连接 /arm/automotive/clocks/interface/iot/memory/mcu/psoc/pmic/touch/usb/wireless PSoC®解决方案 PSoC1|PSoC3|PSoC4|PSoC5LP|PSoC6 赛普拉斯开发者社区 论坛|WICEDIOT论坛|项目|视频|博客|培训|组件 技术支持 /support Allothertrademarksorregisteredtrademarksreferencedhereinarethepropertyoftheirrespectiveowners. CypressSemiconductor198ChampionCourtSanJose,CA95134-1709 ©赛普拉斯半导体公司,2011-2017年。

本文件是赛普拉斯半导体公司及其子公司,包括SpansionLLC(“赛普拉斯”)的财产。

本文件,包括其包含或引用的任何软件或固件(“软件”),根据全球范围内的知识产权法律以及美国与其他国家签署条约由赛普拉斯所有。

除非在本款中另有明确规定,赛普拉斯保留在该等法律和条约下的所有权利,且未就其专利、版权、商标或其他知识产权授予任何许可。

如果软件并不附随有一份许可协议且贵方未以其他方式与赛普拉斯签署关于使用软件的书面协议,赛普拉斯特此授予贵方属人性质的、非独家且不可转让的如下许可(无再许可权)

(1)在赛普拉斯特软件著作权项下的下列许可权(一)对以源代码形式提供的软件,仅出于在赛普拉斯硬件产品上使用之目的且仅在贵方集团内部修改和复制软件,和(二)仅限于在有关赛普拉斯硬件产品上使用之目的将软件以二进制代码形式的向外部最终用户提供(无论直接提供或通过经销商和分销商间接提供),和

(2)在被软件(由赛普拉斯公司提供,且未经修改)侵犯的赛普拉斯专利的权利主张项下,仅出于在赛普拉斯硬件产品上使用之目的制造、使用、提供和进口软件的许可。

禁止对软件的任何其他使用、复制、修改、翻译或汇编。

在适用法律允许的限度内,赛普拉斯未对本文件或任何软件作出任何明示或暗示的担保,包括但不限于关于适销性和特定用途的默示保证。

没有任何电子

设备是绝对安全的。

因此,尽管赛普拉斯在其硬件和软件产品中采取了必要的安全措施,但是赛普拉斯并不承担任何由于使用赛普拉斯产品而引起的安全问题及安全漏洞的责任,例如未经授权的访问或使用赛普拉斯产品。

此外,本材料中所介绍的赛普拉斯产品有可能存在设计缺陷或设计错误,从而导致产品的性能与公布的规格不一致。

(如果发现此类问题,赛普拉斯会提供勘误表)赛普拉斯保留更改本文件的权利,届时将不另行通知。

在适用法律允许的限度内,赛普拉斯不对因应用或使用本文件所述任何产品或电路引起的任何后果负责。

本文件,包括任何样本设计信息或程序代码信息,仅为供参考之目的提供。

文件使用人应负责正确设计、计划和测试信息应用和由此生产的任何产品的功能和安全性。

赛普拉斯产品不应被设计为、设定为或授权用作武器操作、武器系统、核设施、生命支持设备或系统、其他医疗设备或系统(包括急救设备和手术植入物)、污染控制或有害物质管理系统中的关键部件,或产品植入之设备或系统故障可能导致人身伤害、死亡或财产损失其他用途(“非预期用途”)。

关键部件指,若该部件发生故障,经合理预期会导致设备或系统故障或会影响设备或系统安全性和有效性的部件。

针对由赛普拉斯产品非预期用途产生或相关的任何主张、费用、损失和其他责任,赛普拉斯不承担全部或部分责任且贵方不应追究赛普拉斯之责任。

贵方应赔偿赛普拉斯因赛普拉斯产品任何非预期用途产生或相关的所有索赔、费用、损失和其他责任,包括因人身伤害或死亡引起的主张,并使之免受损失。

赛普拉斯、赛普拉斯徽标、Spansion、Spansion徽标,及上述项目的组合,WICED,及PSoC、CapSense、EZ-USB、F-RAM和Traveo应视为赛普拉斯在美国和其他国家的商标或注册商标。

请访问获取赛普拉斯商标的完整列表。

其他名称和品牌可能由其各自所有者主张为该方财产。

文档编号.001-92462版本.*

A 41

更多示例代码?

我们听到了。

要获取更多USBHi-Speed示例代码,请访问网站。

FX2LP™通用可编程接口(GPIF)提供一个独立硬件单元,用于创建数据和控制外部接口所需要的信号。

通过对GPIF寄存器进行CPU读和写操作,GPIF可以移位数据。

本文档通过提供一个简单设计(该设计对GPIF时钟进行2、4和7分频)详细介绍了GPIF单元和它的图形设计工具(称为GPIFDesigner)。

在配置和管理该接口时,仅需要三行C代码。

本应用笔记还提供了一个示例,用于演示了如何将USB连接添加到GPIF设计。

目录 1简介..........................................................................12FX2LP架构概述.......................................................2 2.1端口模式..........................................................22.2从设备FIFO模式.............................................22.3GPIF模式—自动............................................22.4GPIF模式—手动............................................33通用可编程接口........................................................33.1GPIF概述........................................................33.2物理互连..........................................................44创建一个GPIF应用..................................................54.1设计GPIF接口................................................54.2使用固件框架...................................................54.3使用GPIFDesigner实现GPIF波形................65示例1:对GPIF时钟进行2分频和4分频...............66示例2:对GPIF时钟进行7分频...........................167示例3:使用单个字的读/写数据操作......................18 8USB数据流............................................................21 9设计GPIF互联.......................................................21 9.1单字写波形.....................................................23 9.2单字读波形.....................................................27 9.3单个字操作的固件编程...................................30 9.4代码段............................................................31 9.5运行GPIF单个字操作示例............................36 9.6单个字操作的逻辑分析仪波形........................37 10 相关文档.............................................................39 10.1其他GPIF示例..............................................39 10.2参考设计........................................................39 10.3数据手册........................................................39 11 总结....................................................................39 文档修订记录...................................................................40 全球销售和设计支持........................................................41 1简介 USB2.0的480Mbps信号速率要求控制器芯片对高速数据进行输出/输入传输。

提供了一个独立的硬件单元,CPU通过对其进行相关设置实现USB端点FIFO和外部接口之间的数据直接传输。

外部接口可以是RAM、FIFO或第二个处理器。

因此,CPU不需要移动数据。

配置时,由于数据经过了GPIF硬件通道,因此CPU仅控制各标志和中断。

通过使用GPIF可以实现各种协议,包括增强型IDE(EIDE–有时成为快速ATA或快速IDE)或ATA数据接口(ATAPI)打印机,并行接口(IEEEP1284),以及ia.ThisdocumentdescribesthearchitectureandimplementationoftheFX2LPGPIF.本文档对FX2LPGPIF的架构和实现进行了说明。

介绍了应用使用模型和调试决策,并提供了各种示例用于介绍和解释GPIF概念。

文档编号.001-92462版本.*

A 1 EZ-USB®FX2LP™GPIF入门 2FX2LP架构概述 EZ-USBFX2LP是一个灵活的USB2.0外设控制器,用于处理USB2.0的最大宽度。

FX2LP通过提供GPIF为外部器件提供高速并行接口,从而优化USB的吞吐量。

通过使用该GPIF,可以在FX2LP端点FIFO和GPIF接口间传输数据。

以下各节通过提供可配置的不同FX2LP模式,对FX2LP架构进行了简要说明。

2.1端口模式 FX2LP拥有24个接口引脚,根据模式设置,可将这些引脚用于各种目的。

在“端口”模式下,它们是通用的I/O引脚,并且GPIF无效(图1)。

图

1.端口模式下的FX2LP Host(PC) USBSIE FIFOs 8051 FX2LP Pins PA[7:0]PB[7:0]PD[7:0] 2.2从设备FIFO模式 在从设备FIFO模式中,专用的FX2LP逻辑提供了控制和数据信号,用于将USB端点FIFO连接到外部FIFO控制器。

除了数据总线和FIFO选择输入外,该接口还提供了常用的FIFO信号,如RD、WR和FIFO标志。

更多有关该接口的详细信息,请参考赛普拉斯应用笔记AN63787-EZ-USBFX2LPGPIFandSlaveFIFOConfigurationExamplesUsing8-bitAsynchronousInterface. 图

2.从设备FIFO模式下的FX2LP引脚 Host(PC) USBSIE FIFOs 8051 FX2LP Pins SlaveFIFOlogic CLKRD,WRFLAGS DATA[15:0]ADDR[1:0] Control 2.3GPIF模式—自动 当GPIF有效时,接口引脚作为主设备控制外部外设,如RAM、FIFO或外部处理器。

GPIF可在两个子模式下运行:自动模式和手动模式。

在自动模式下,数据从端点FIFO直接输送到外部接口。

8051配置和监控该接口,但不会直接访问FIFO数据;请参考图

3. 图

3.GPIF自动模式下的FX2LP Host(PC) USBSIE FIFOs 8051 FX2LP PinsGPIF IFCLKCTL[5:0]ADDR[8:0]DATA[15:0]RDY[5:0]Gstate[2:0] 文档编号.001-92462版本.*

A 2 EZ-USB®FX2LP™GPIF入门 赛普拉斯应用笔记AN57322-InterfacingSRAMwithFX2LPoverGPIF来说明GPIF自动模式。

该笔记介绍了如何使用8位异步接口和GPIF自动模式将赛普拉斯CY7C1399BSRAM连接至FX2LP。

2.4GPIF模式—手动 在手动模式下,通过使用GPIF寄存器的读和写操作,8051对该接口进行读写字节(图4)。

在本文档的后续内容中介绍了GPIF手动模式的一个示例。

示例3:使用单个字的读/写数据操作. 图

4.GPIF手动模式下的FX2LP Host(PC) USBSIE FIFOs 8051 FX2LP PinsGPIF IFCLKCTL[5:0]ADDR[8:0]DATA[15:0]RDY[5:0]Gstate[2:0] 3通用可编程接口 3.1GPIF概述 GPIF的内核是一个可编程状态机,用于控制8位或16位双向数据总线,并生成多达六个控制(CTL)和九个地址(GPIFADR)输出。

另外,它还接收六个外部和两个内部READY输入,用以确定分支条件。

用户定义的四个波形描述符控制该状态机;8051程序会选择四个波形中的某一个在给定的时间内有效。

每个GPIF波形描述符包含多达七种状态,名称分别为S0-S6。

预定义的S7用于表示闲置状态。

在每个状态内,您可以将GPIF编程为: ▪使某些或所有CTL输出驱动高电平、驱动低电平或悬空▪采样或驱动8/16位数据总线▪递增GPIF地址总线的值▪递增FIFO指针▪向8051触发一个GPIF波形中断 每个状态中的分支决策是通过下列选项得到的两个信号的逻辑AND、OR或XOR: ▪六个READY输入引脚▪内部FIFO标志▪内部RDY标志▪内部事务处理终止标志 通过两个已选信号的逻辑结合可确定下一个状态。

另外,计算好可编程延迟后,状态机会转入下一个状态。

该延迟的范围为1到256个时钟周期。

采样和分支的状态被称为“决策点”。

不带决策点的所有状态仅会维持一个时钟间隔,在下一个时钟间隔内,它将自动转到下一个状态。

文档编号.001-92462版本.*

A 3 图

5.GPIF状态机句法A(func)BisFALSE EZ-USB®FX2LP™GPIF入门 _TRIGCPU IDLE State7 NonDecision Point DecisionPoint State0 State1 A(func)BisTRUE (func)=AND,OR,XOR 3.2 3.2.1 3.2.23.2.33.2.43.2.53.2.6 图5中的状态机的流程如下所示:

1.从闲置状态开始,等待CPU_TRIG信号激活。

2.激活CPU_TRIG时,转入状态0;在该状态中,您可以激活某些控制信号输出,移动数据或递增地址总线。

该状态仅在下一个时钟前持续,因为没有任何决策,所以下面它会无条件地转入状态

1。

3.并保持状态

1,直到两个信号A和B的逻辑组合为真为止(即它为错误时)。

例如,要想一直保持状态

1,直到READY信号有效或完成一个计数为止,那么需要选择A代表READY输入,并选择B代表一个计数器到期。

如果发生两个条件其中一个(READY或终端计数),状态机可通过使用逻辑运算符OR输出状态

1。

4.当该条件为真时,将转入闲置状态。

状态机也随即停止。

物理互连 GPIF互连包含一个8位或16位的数据总线、地址总线、控制输出和就绪输入(图4)。

另外它还包含了三个GSTATE输出(用于指出GPIF机械的当前状态),用于调试目的。

本节详细说明了这些信号。

IFCLKIFCLK(接口时钟)是所有GPIF操作的参考时钟。

可将其作为输入或输出信号使用;并且您可以将上升沿或下降沿选为有效沿。

当作为输入信号使用时,可以使用一个频率为5MHz到48MHz的外部时钟驱动它。

作为输出信号使用时,可以使用FX2LP中一个频率为30MHz或48MHz的内部时钟进行驱动IFCLK。

如果外部外设需要的时钟频率更低,那么可以使用FX2LP的内部时钟切换各CTL线中的某一个。

在第一个示例中,GPIF时钟被2分频和4分频,并通过使用两个CTL输出可以输出这些信号。

如果需要进行更高的分频,请在进入下一个状态前,通过编程GPIF状态计算已编程的时钟数量(1到256)。

GPIFADR[8:0](仅输出)GPIF通过驱动GPIFADR[8:0]为需要地址行的外设提供地址行。

在所有GPIF状态下,可以保持或递增这些输出。

FD[15:0](双向)该数据总线是一个通道,通过它可以在FX2LP端点FIFO和外部外设间传输负载数据。

该信号经配置后可作为8位或16位接口运行。

系统需要时,可进入三态。

在16位模式下,FD[7:0]代表端点FIFO的第一个字节,而FD[15:8]则代表第二个字节。

CTL[5:0](仅输出)控制输出信号可提供外部外设所需要的各种信号,如读/写选通、使能和分频时钟。

RDY[5:0](仅输入)就绪输入信号提供了外部外设的状态信息,如FIFO状态标志和有效数据。

GPIF能将这些信号作为决策点限定符使用。

GSTATE[2:0](仅输出)调试输出信号代表在GPIF波形中执行的状态。

这些信号与逻辑分析仪相连,以用于调试目的。

文档编号.001-92462版本.*

A 4 EZ-USB®FX2LP™GPIF入门 4创建一个GPIF应用 本节介绍了创建GPIF应用的各步骤。

4.1设计GPIF接口 要设计GPIF互连,您需要了解FX2LP和外部外设器件之间的接口。

通过使用FX2LP数据手册和技术参考手册可以定义该接口。

ThefollowingdecisionsdeterminehowtoconfiguretheGPIF. ▪8位或16位数据路径? 该决定通常取决于外设提供的数据路径的大小。

如果大小为16位,则可以使用该路径尽可能扩大物理接口的带宽。

对于16位的数据路径,当连接至数据总线时,需要考虑字节顺序(字节次序)和位编号。

▪外部还是内部接口时钟? 决定取决于外设操作模式的灵活度。

例如,如果它可以接收一个频率为30或48MHz的外部时钟输入,那么内部GPIF时钟便能与外设时钟输入相连。

▪是否需要地址行? 如果在读/写周期操作期间,外设要求对任何寄存器或存储器位置进行寻址,则可以使用GPIFADR[8:0]。

▪控制行 从CTL[5:0]指定GPIF控制输出。

在这些操作中,外设可能需要读/写信号、芯片选择和其他控制输入。

确定有哪些输入,并合理分配CTL[5:0]。

通过GPIFDesigner工具,您能够更清晰地命名这些信号;例如CTL[0]的WR#和CTL[1]的RD#。

▪状态(RDY)行 确定在读/写周期期间需要监控的状态信号数量。

指定包括哪些状态信号,并合适分配RDY[5:0]。

GPIFDesigner工具会再次允许您命名这些信号,以便使这些名称符合您的设计。

▪接口时序 分配输入和输出之后,GPIF应用的主要任务是设计时序波形,从而考虑接口时序。

注意:并非所有FX2LP封装类型均提供GPIF接口信号的完整集。

例如,100引脚和128引脚的FX2LP封装提供了所有六个就绪输入(RDY[5:0])和控制输出(CTL[5:0])。

56引脚封装提供了两个RDY信号RDY[1:0]和三个CTL信号CTL[2:0]。

4.2使用固件框架 使用GPIFDesigner创建接口信号和波形时,您需要使用Keil集成开发环境(IDE)对控制固件进行编写。

开始操作新的FX2LP固件项目时,优先使用基于赛普拉斯编写的固件框架的KeiluVision2项目。

FX2LPDevelopmentKit(DVK)所提供的固件示例都是基于框架的。

您可以使用这些示例其中的任何一个进行操作,或将Keil项目复制到新的子目录内,以进行修改。

这样,您便能够对空的固件基础进行操作。

如果使用了固件框架项目,那么您可以集中到您的应用代码,因为已经写入了USB低电平协议代码。

更多有关信息,请参考fw.c文件和开发套件文档。

应用方案拥有两个主要组件: ▪配置GPIF和启动GPIF传输的固件。

该固件还会执行其他应用任务,如USB枚举和端点配置。

▪实现物理总线时序和数据流的GPIF波形描述符。

该固件包含五个文件:fw.c、periph.c(可以重新命名该文件)、dscr.a51、ezusb.lib和usbjmptb.obj。

这些文件拥有KeiluVision2固件框架项目。

第二个组件是一个包含了代码的C源文件(例如,gpif.c),它用于定义GPIF波形和初始化GPIF单元。

当您通过图形方式定义接口后,GPIFDesigner工具将创建该C文件。

这样便不用知道GPIF单元中的单独寄存器和位。

您可以在此处下载GPIFDesigner工具。

文档编号.001-92462版本.*

A 5 EZ-USB®FX2LP™GPIF入门 4.3使用GPIFDesigner实现GPIF波形 GPIFDesigner生成包含了GPIF波形描述符的C代码,使用这些描述符可以实现接口的物理总线时序。

GPIFDesigner可实现多个波形性能,包括四种波形类型:单写、单读、FIFO写和FIFO读。

CPU通过写入GPIFWFSELECT寄存器控制所使用的波形。

每一个描述符的长度均为32个字节,它位于片上存储器空间内专用的GPIF波形描述区域内。

通过GPIFDesigner工具,您可以将这些描述符作为“黑箱子”使用。

这是因为它可以生成所有需要的C代码,用于实现和使用这些描述符。

将这些GPIF波形作为状态机使用。

存在七种状态或间隔(S0-S6),以及一个用于终止操作的自动闲置状态S7。

图

6.由各状态构成的GPIF波形 将这些GPIF波形作为状态机使用。

存在七种状态或间隔(S0-S6),以及一个用于终止操作的自动闲置状态S7。

图6显示的是一个示例,它说明了一个简单的波形被分解为各GPIF状态转换。

5示例1:对GPIF时钟进行2分频和4分频 首先,需要设计一个状态机用于对GPIF时钟进行2分频和4分频,然后在CTL[0]和CTL[1]上分别输出分频后的时钟信号。

这样,在介绍高级特性包括USB端点FIFO前,可以了解GPIFDesigner工具的基本知识。

由于在本示例中没有使用USB,因此不需要固件框架。

1.解压并存储随本应用笔记附带的FX2LPsourcecodeandGPIFprojectfiles.zip文件。

转到FX2LPSource codeandGPIFprojectfiles\Firmware\GPIFClockDivider。

右击该文件夹并单击Properties(属性)项。

如果选择了“Read-only...”项,请取消勾选它。

点击OK,以允许子目录采用修改内容。

在该文件夹内,双击GPIF_Clock_Divider.uv2。

它包含一个基本的GPIF项目,此项目包含所有信息,但不包括GPIF信息。

双击main.c文件以打开它;您将看到仅需要三行代码便能够启动GPIF操作: WORDg_data;GpifInit();XGPIFSGLDATLX=g_data;//Starttransfer 文档编号.001-92462版本.*

A 6 图

7.基本的GPIFKeil项目 EZ-USB®FX2LP™GPIF入门 如果您没有修改任何代码,您会看到链接器错误,这是因为GPIFKeil项目未包含GPIFDesigner生成的GPIFC文件。

该文件包含GpifInit()函数和波形表数据。

下一步骤将创建该文件。

2.启动GPIFDesigner,然后依次选择File>New打开下面图片显示的窗口。

图

8.GPIFDesigner启动窗口

3.要想使用FX2LP开发板检测该示例,请选择CYFX2(128引脚)并点击OK。

这样可打开框图窗口: 文档编号.001-92462版本.*

A 7 图

9.GPIFDesigner框图 EZ-USB®FX2LP™GPIF入门

4.该框图顶部,右击Clk48MHz文本框配置GPIF时钟。

对于该项目,则保持默认设置。

图10.IFCLK默认设置

5.右击ADR(地址)标签。

该示例没有使用地址总线,因此您可以点击DisableAll;这样会使框图内的各地址行变暗。

文档编号.001-92462版本.*

A 8 图11.禁用地址行 EZ-USB®FX2LP™GPIF入门

6.通过右击RDY(就绪)标签配置六个RDY输入。

该示例没有使用RDY输入,因此未选中这些输入。

要取消选择RDY5,请先取消选择SubstTCforRDY5. 图12.禁用RDY输入

7.通过右击CTL(控制)标签进行配置六个CTL输出。

按照下图设置这些输入。

文档编号.001-92462版本.*

A 9 图13.CTL输出设置 EZ-USB®FX2LP™GPIF入门 将两个输出重新命名为divby2和divby4,并将这两个名称输入到文本框内。

推荐命名您的信号,这是因为它们会更新所有GPIFDesigner屏幕中的标签,从而更容易识别这些信号(例如,divby4而不是CTL1)。

现在该框图会显得更加简单。

图14.时钟分频器框图

8.选择SingleWrite选项卡,以进行绘制两个波形。

右击该选项卡的名称,选择SelectTabLabel,并将其重新命名为Divider。

您会看到一个空白波形的编辑界面,如图15所示。

文档编号.001-92462版本.*

A 10 图15.空白波形编辑器界面 EZ-USB®FX2LP™GPIF入门

9.该状态机有一个名称为IDLE(闲置)的状态。

要想添加某个状态,需要点击CTL带(divby2和divby4)中的某一个。

另外,您还可以通过点击数据带添加各种状态,但该设计不使用数据总线。

在divby2带中,点击第二个垂直虚线。

图16.第一个波形切换 出现的三角形表示GPIFDesigner已经添加了状态s0,并在其开始和结束时切换了divby2输出。

10.现在,请在后面每三个时钟切换虚线上点击divby2波形,这样可创建2分频时钟。

文档编号.001-92462版本.*

A 11 11.在divby4波形中,点击第二个和第四个时钟线。

您的屏幕将显示图17.图17.2分频和4分频波形 EZ-USB®FX2LP™GPIF入门 注意:可通过右击任何一个三角形来修改它的逻辑状态,从而修改信号属性。

另外,通过横向拖动这些三角形,以使某个状态持续时间大于一个时钟。

图17中显示的状态机启动时,它将在每个时钟上升沿上从s0状态依次转到s1、s2和s3,然后以闲置状态停止。

您需要重复该过程;也就是说s3始终要返回到s0状态。

为此,在状态线中将添加一个‘决策点’。

图18.第一个决策点 文档编号.001-92462版本.*

A 12 EZ-USB®FX2LP™GPIF入门 12.点击s2和s3状态之间的状态区间。

这样可添加一个作为决策点的菱形,并显示一个窗口用于配置该决策。

要想进行一个无条件反转,您可以从下拉列表顶部选取两个逻辑信号以及它们的逻辑运算符。

您需要指定THEN和ELSE条件,以切换到S0状态。

也就是要无条件反转到S0状态。

每次进入该状态,可以使用LOOP(Re-Execute)复选框重新激活状态条件。

s3状态中不存在“保持该状态直到发生变化”循环,因此可以取消勾选该项。

在状态s3中,时钟波形显示一个对角线以表示未知决策状态的时钟数量。

这是因为时钟数量取决于满足转换条件的时间。

追踪该设计使用的所有参数,并进行相应的选择项更新。

例如,如果您添加了一个状态s4,那么它将自动被添加到GOTO选项内。

注意:决策点位于状态的开始位置,而不是结束处(决策点在该状态下发生)。

因此,菱形位于s3开始的位置。

13.要存储GPIFDesigner项目,请依次选择File>SaveAs并将该项目存储在Keil项目文件夹asDiv_2_4.gpf内。

如果您想修改当前波形,你可以重新打开该文件。

要存储GPIFDesigner生成的C代码,请依次选择Tools>ExporttoGPIF.cfile并将该代码存储在Keil项目文件夹GPIF_div_2_4.c内。

Div_2_4.gpf和GPIF_div_2_4.c同样也在FX2LPSourcecodeandGPIFprojectfiles\GPIFClockDivider\GPIF_div_2_4文件夹内提供。

通过使用这些文件,您可以直接测试该项目。

14.最后一步是将GPIFDesignerC文件添加到Keil项目。

右击SourcesGroup1并选择Addfiles….找到Keil项目文件夹并添加GPIF_div_2_4.c文件。

图19.将GPIFDesignerC文件添加到Keil项目 15.编译该项目。

KeilIDE编译并链接这些文件,然后通过调用‘hex2bix’工具将负载模块转换为一个与赛普拉斯USB控制面板加载程序相兼容的格式。

按照下列步骤进行操作,您可以在FX2LP开发板上尝试执行该设计:

1.关闭EEPROMSELECT开关。

以使能FX2LP片上的USB代码加载程序。

文档编号.001-92462版本.*

A 13 EZ-USB®FX2LP™GPIF入门

2.将FX2LP板插入到PCUSB端口。

如果是第一次操作,您会看到弹出消息,提示您安装USB驱动程序。

请找到C:\Cypress\USB\CY3684_EZ-USB_FX2LP_DVK\1.0\Drivers\cyusbfx1_fx2lp,然后选择对应WindowsOS的文件夹。

您可以通过查看WindowsDeviceManager(Windows器件管理程序)来确认驱动程序是否安装成功: 图20.赛普拉斯USB加载驱动程序已安装

3.在C:\Cypress\CypressSuiteUSB3.4.7\CyUSB.NET\bin\CyControl.exe中启动USB控制面板。

4.在左侧面板上,您可看到FX2LP板以及与其相连的其他USB器件。

如果仅需查看FX2LP板,则在右侧面板上点击DeviceClassSelection选项卡,并取消勾选除DevicesservedbytheCyUSB.sysdriver(oraderivative)外的所有选项。

左侧面板如图21所示。

图21.USB控制中心内的FX2LP板

5.现在您可以将Keil编译的十六进制文件加载到该板上。

加亮显示EZ-USB输入并选择ProgramFX2>RAM. 文档编号.001-92462版本.*

A 14 图22.将新器件代码加载到RAM EZ-USB®FX2LP™GPIF入门

6.按下FX2LP开发板上的RESET按键,以使能USB加载程序。

7.找到Keil项目文件夹并选择Keil编译器的结果GPIF_Clock_Divider_Proj.hex.8.用探针检测P2引脚11(CTL0=divby2)和P2引脚10(CTL1=divby4)。

此时,您可以看到如图23所示的 波形。

图23.进行2分频和4分频后的GPIF48MHz时钟 文档编号.001-92462版本.*

A 15 EZ-USB®FX2LP™GPIF入门 6示例2:对GPIF时钟进行7分频 通过修改示例

1,您可以选择任何时钟分频器,即使使用的是奇数除数的时钟。

1.启动GPIFDesigner;依次选择File>New来创建GPIF项目。

选择CYFX2(128pin)器件。

2.清除先前描述的ADR和RDY信号,并将CTL0重新命名为divby7,然后将CTL1重新命名为stb。

禁用其他四个 信号。

图24.两个输出:7分频和探针

3.选择SingleWrite选项卡。

在divby7带中,在第一个三角形后面的三个时钟位置上放置一个状态转换三角形,并在其后面四个时钟所在的位置上放置另一个三角形。

在离stb带开始后一个时钟的位置上放置一个三角形;右击第一个三角形,并将它设置为HI;将第二个三角形设置为LO。

这样会将负极性脉冲转换为状态s0中的正极性脉冲。

这时,波形如图25所示。

图25.7分频和探针波形

4.最后,点击时钟线上的状态带,该线同状态s2结束前面一个时钟的位置相对应。

这样可以创建决策点和新状态s3。

应该将该决策点配置为无条件转换到状态S0。

由于THEN和ELSEGOTO的状态都是S0,因此IF条件不重要——您可以从下拉列表中选择任何IF条件。

文档编号.001-92462版本.*

A 16 图26.无条件转换到S0 EZ-USB®FX2LP™GPIF入门 图27.进行7分频的最后波形

5.将该文件(Tools>ExporttoGPIF.c)导出到Keil项目文件夹内,并将它命名为GPIF_div_7.c。

将该项目文件(File>SaveAs)保存为Div_by_7.gpf。

Div_by_4.gpf和GPIF_div_7.c文件也在FX2LPSourcecodeandGPIFprojectfiles\GPIFClockDivider\GPIF_div_7文件件中提供。

您可以直接使用这些文件,进行该项目的测试。

6.在KeilFiles选项卡中,右击SourceGroup1,点击AddFiles…并将GPIF_div_7.c添加到该项目内。

现在您拥有两个GPIF波形文件,因此Keil编译器需要确定将要使用的文件。

要想禁用编译中的任何源文件,需要右击它,选择Optionsforfile…,并取消勾选IncludeinTargetBuild复选框。

如果您的项目中拥有多个GPIF.c文件,请确保仅勾选其中一项。

7.选择Project>RebuildAllTargetFiles,进行重新编译。

8.按下FX2LP开发板上的RESET,这样可以恢复USB代码加载程序的状态。

9.使用USB控制中心面板加载新编译的GPIF_Clock_Divider_Proj.hex文件。

10.探针P2引脚11(CTL0=divby7);您的屏幕将如图28所示。

文档编号.001-92462版本.*

A 17 EZ-USB®FX2LP™GPIF入门图28.顶部:7分频;底部:stb信号的宽度为一个时钟,以用于参照目的 如果您需要更长的时钟分频(如87分频),将如何进行?GPIFDesigner允许您设置一个状态的持续时间为1到256个时钟。

点击状态带中的任何状态;将出现如图29中所示的窗口。

点击SetStateDuration,然后设置时钟数量(图30)。

当您对某个状态的时钟数量进行手动设置时,时序框图的时钟线将不再指出该状态的时钟数。

图29.s2状态的属性 图30.选择1到256个时钟周期 7示例3:使用单个字的读/写数据操作 在该示例中,FX2LP数据通过赛普拉斯CY7C4265-15AXC外部FIFO进行循环。

该示例使用GPIF手动模式并通过一个16位数据总线进行单次的读/写GPIF数据操作。

您可以使用示波器或逻辑分析仪监控FIFO写操作,但在检测读操作时,您需要将外部FIFO芯片连接至FX2LP开发板。

例如,使用开发套件所提供的原型电路板将外部FIFO安装到FX2LP开发板上。

如需了解外部FIFO的全部硬件规范,请下载CY7C4265数据手册。

通过单次读/写操作可在FX2LP和外设之间传输一个字节/字的数据。

与FIFO读/写操作相比,这些操作更简单,因此应该优先执行这些操作。

如果在GPIF开发周期中您先执行该步骤,那么在处理更复杂的设计前,您需要验证系统的所有部分(硬件、固件、软件)。

在验证完物理互联和基本数据传输后,应该转到完整的设计。

文档编号.001-92462版本.*

A 18 EZ-USB®FX2LP™GPIF入门 7.1.17.1.2 执行FIFO读/写操作执行完单次操作后,需要执行GPIFFIFO读/写操作,以增大带宽。

先实现FIFO写波形可避免检测整个环回方案时遇到问题;如果它不工作,那么很难区分该问题是读操作、写操作还是两个操作。

需要时进行优化生成GPIF波形时,要先设置物理总线为高电平的时间。

这样可以缩短每个GPIF操作的循环时间,同时仍可满足外设所要求的时序参数。

您还可以对该设计进行修正,以提高固件代码的效率,并改进本阶段的整体固件代码流。

图31通过使用GPIF设计流程图对本章进行了总结。

图31.GPIF设计流程图 DesignGPIFInterconnect UseFirmwareFrameworks 8-or16-bit?

InternalorExternalIFCLK?

No.ofGPIFADR[8:0] Lines?

No.ofCTL[5:0]Lines?

No.ofRDY[5:0] Lines?

OtherI/OLines?

ImplementGPIFWaveformDescriptors ImplementSingleRead/WriteTransactions IntegrateandTest No CompletedatapathverifiedandPhysicalinterconnectfleshedout?

Yes NoImplementFIFORead/WriteTransactions IntegrateandTest Completedatapathverified?

Yes OptimizeifNecessary 文档编号.001-92462版本.*

A 19 EZ-USB®FX2LP™GPIF入门 7.1.3 将FIFO连接至FX2LPGPIF接口显示的是FX2LP与外部FIFO之间的连接。

FX2LP使用其双向总线FD[15:0]对外部FIFO中的数据进行读写。

通过将FIFO的输出数据总线Q[15:0]和输入数据总线D[15:0]连接在一起,可将FIFO数据总线设置为双向。

该示例通过USBBULK传输对FIFO数据进行读写。

使用SuiteUSB3.4-USBDevelopmenttoolsforVisualStudio所提供的USB控制中心,可以执行这些传输。

表1对GPIF互联进行了详细说明。

指定CTL和RDY引脚与最小FX2LP封装(包含56个引脚)相兼容。

图32.GPIF与外部同步FIFO间的连接 FX2LPIFCLK CY7C4265-15ACRCLKWCLK FD[15:0] DATA[15:0]D[15:0] CTL0CTL1CTL2 RDY0RDY1 PA2 DATA[15:0]Q[15:0] WEN#REN#OE# EF#FF# RS# FX2LPGPIF信号IFCLK FD[15:0] CTL0CTL1CTL2 CY7C426515AXC信号WCLK,RCLK D[15:0],Q[15:0] WEN#REN#OE# 表

1.分配至CY7C4265-15AC信号的FX2LPGPIF信号 说明 IFCLK连接到外部FIFO的读写时钟输入(WCLK、RCLK)。

确认WEN#时,数据在每个WCLK上升沿上为外部FIFO提供时钟脉冲。

同样,确认REN#和OE#时,FIFO在RCLK每个上升沿上的Q[15:0]显示数据。

外部FIFO可接受最大为66.7MHz的输入时钟频率,因此,能够处理的输入IFCLK频率为30MHz或48MHz。

请注意井字符(例如OE#)表示低电平有效。

GPIF数据总线(FD[15:0])连接至外部FIFO的输入数据总线(D[15:0]),以进行字操作。

外部FIFO的输出数据总线Q[15:0]也被连接至GPIF数据总线,以便FX2LP可以读回数据内容。

由于两个单向FIFO数据总线彼此连接,因此GPIF必须控制OE#信号,以避免发生总线冲突。

特别是当FX2LP驱动数据总线时,不能将OE#置于低电平状态—这是因为FX2LP和FIFO同时驱动数据总线时,会导致总线冲突。

CTL0连接至外部FIFO写使能引脚WEN#。

GPIF将WEN#置于低电平时,在每个WCLK上升沿上将数据写入到外部FIFO内。

CTL1连接至外部FIFO读使能引脚REN#。

当GPIF将REN#和OE#置于低电平时,FIFO在RCLK的每个上升沿上驱动Q[15:0]中的数据。

CTL2连接至外部FIFO输出使能引脚OE#。

将REN#和OE#置于低电平时,FIFO在RCLK的每个上升沿上驱动Q[15:0]上的数据。

文档编号.001-92462版本.*

A 20 EZ-USB®FX2LP™GPIF入门 FX2LPGPIF信号 RDY0 CY7C426515AXC信号 EF# RDY1 FF# PA2 RS# 说明 RDY0连接至外部FIFOEMPTY标志EF#,如果FIFO为空,它将置于低电平。

由于能够在GPIF转换状态中检测READY信号,因此从外部FIFO读取数据时,GPIF可以使用该信号进行控制数据传输。

RDY1连接至外部FIFOFULL标志FF#,如果FIFO已满,它将置于低电平。

当写入外部FIFO时,GPIF可使用该信号控制数据传输。

PA2连接到外部FIFORESET引脚。

PA2是一个FX2LPGPIO引脚,并且不属于GPIF逻辑。

在启动GPIF数据传输前,8051代码会使用PA2将外部FIFO复位到一个已知状态。

8USB数据流 USB端点2OUT(EP2OUT)作为GPIF写入外部FIFO的发送端点使用,端点6IN(EP6IN)作为GPIT从外部FIFO读取的接收端点使用。

从主机端的角度来看,USBIN和OUT方向如下: ▪EP2OUT包含了USB主机(PC)发送和FX2LP接收的数据包。

▪EP6IN包含了FX2LP发送和PC接收的数据包。

9设计GPIF互联 通过使用第一个示例中所描述的GPIF各步骤可以设置GPIF互联,具体如下。

1.启动赛普拉斯GPIFDesigner工具。

2.请依次选择File>New,然后选择FX2LP开发板使用的CYFX2(128pin)。

3.右击外部器件模块中的Un-named标签并将其重新命名为CY7C4265-15AC.4.默认情况下,数据总线被配置为16位。

该示例使用了16位数据总线。

5.右击ADR标签。

该设计没有使用地址行,因此可禁用它们以简化框图。

6.右击RDY标签,并对RDY信号进行配置,如图33中所示。

图33.RDY引脚配置

7.右击CTL标签,并对CTL信号进行配置,如图34所示。

文档编号.001-92462版本.*

A 21 图34.CTL引脚配置 EZ-USB®FX2LP™GPIF入门 .8.右击48MHzCLK文本框,并按照图35的内容配置时钟属性。

选择InvertClock复选框。

GPIF更改并采样时钟 上升沿上的信号;FIFO将更改并采样时钟下降沿上的信号。

这个半时钟偏移提供了各种接口时序设置和保持时间。

图35.配置IFCLK 该框图将如图36所示。

现在,该时钟被标签为“nClk48Mhz”,其中“n”表示时钟反转。

图36.FIFO的配置接口 文档编号.001-92462版本.*

A 22 EZ-USB®FX2LP™GPIF入门 9.1单字写波形 通过写波形,可以将数据从FX2LPOUT端点FIFO传输到外部FIFO。

右击FIFORead选项卡并将其重新命名为“Unused”。

对FIFOWrite选项卡进行类似操作。

您的屏幕将如图37所示。

图37.波形屏幕 请依次点击Tools>MapWaveforms进行WFSELECT(选择波形)(图38)。

图38.波形映射对话框 请确保单写波形被映射到SINGLEWR,而单读波形被映射到SINGLERD。

这样可对8051寄存器进行配对(这些寄存器将这些波形设置为GPIF命名的波形)。

注意:波形映射允许您为同一类传输定义多个波形组。

例如,您可以将两种不同的波形类型使用在单写操作中。

通过写波形可以管理各字节传输,这些字节传输将FX2LPOUT端点的数据传输到外部FIFO。

要想创建FIFO写波形,请先检查CY7C4265数据手册中提供的CY7C4265FIFO的写周期时序。

图39显示的是写周期时序,其中GPIF状态被添加到该框图的底部。

文档编号.001-92462版本.*

A 23 图39.写周期时序框图 EZ-USB®FX2LP™GPIF入门 IDLE S0 S1 在写周期时序框图中,您可以创建如图40.图40.单字FIFO写状态框图 S0 WEN#=0REN#=1OE#=1Activate Data S1 WEN#=1REN#=1OE#=1Deactivate Data Initiate S7(IDLE) WEN#=1REN#=1OE#=1Deactivate Data ▪对于单写波形,通过将WEN#逻辑置于低电平和驱动数据总线,可以在状态S0期间将数据写入到外部FIFO内。

文档编号.001-92462版本.*

A 24 EZ-USB®FX2LP™GPIF入门 ▪在状态S1内,WEN#被禁用(为高电平),并且GPIF数据总线停止驱动(悬空)。

S1是一个决策点状态,它会强制无条件转换到闲置状态,从而停止波形。

闲置状态下并没发生任何活动 ▪每次触发单写波形时,GPIF引擎都会经过S0、S1,然后停止于S7(空闲)。

请按照下列各步骤完成单写波形。

1.点击SingleWrite波形选项卡。

2.点击离左边界一个时钟周期的WEN#跟踪,在此处放置一个操作点并创建WEN#波形。

自动生成状态0(s0), 并会持续一个IFCLK周期(20.83ns)。

3.由于GPIF被写入到外部FIFO,因此在波形期间,必须将REN#和OE#置于高电平,为防止外部FIFO驱动它的 数据总线。

为此,需要右击OE#和REN#跟踪上的操作点,并选择High

(1)。

各波形如图41所示。

图41.WEN#在一个时钟内保持低脉冲

4.必须将数据总线驱动到s0状态。

因此,需要右击数据操作点,并选择ActivateData. 应该只在一个时钟周期内驱动数据总线。

经过一个时钟周期后,要想停止驱动数据,需要在数据带中距离第一个时钟一个时钟的位置上放置另一个操作点。

请注意,现在数据带只在s0期间保持为高电平。

各波形如图42中所示。

文档编号.001-92462版本.*

A 25 图42.S0期间,会在一个时钟周期内驱动数据 EZ-USB®FX2LP™GPIF入门

5.通过创建一个决策点状态S1可以返回闲置状态。

在S0状态的右边界上点击状态带,然后按照图43中显示的内容设置无条件转换。

图43.无条件转换到闲置状态 单个字写波形如图44所示。

图44.单子写波形 文档编号.001-92462版本.*

A 26 EZ-USB®FX2LP™GPIF入门 9.2单字读波形 通过读波形可以管理从外部FIFO到FX2LPIN端点将FIFO的字节传输。

类似于写周期,GPIF波形必须满足外部FIFO时序的要求。

首先,需要检查外部FIFO的读周期时序,然后创建单读状态机。

图45显示的是CY7C4265的读周期时序,其中GPIF状态被添加到该框图的底部。

图45.读周期时序框图 S0 S1 S2 通过时序信息您可以创建如图46所示的状态机,以用于字节读操作。

. 图46.字节读状态框图 S0 WEN#=1REN#=0OE#=

1 S1 WEN#=1REN#=1OE#=

0 Initiate S7(IDLE) WEN#=1REN#=1OE#=

1 S2 WEN#=1REN#=1OE#=0ActivateData 文档编号.001-92462版本.*

A IDLE 27 EZ-USB®FX2LP™GPIF入门 ▪对于单读波形,在S0状态期间,REN#在一个IFCLK周期内保持逻辑低电平状态。

这样会在确认OE#前,外部FIFO需要记录在数据手册中的tENS设置时间。

经过一个时钟后取消确认REN#可确保FIFO未递增一个字,以执行读操作。

▪然后S1将确认OE#并转到S2状态。

▪由于它需要进行反转,因此S2作为决策点状态。

S1状态开始阶段,仍无法从外部FIFO获得数据,因此,GPIF 只能在S2开始时“采样”数据。

▪每次触发单读波形时,GPIF引擎都会按S0、S1、S2和S7的顺序循环。

请按照下列各步骤创建单读波形。

1.点击SingleRead波形选项卡。

2.右击REN#跟踪中的第一个时钟,并选择Low

(0)。

点击离左边界一个时钟周期的REN#跟踪,在此放置一个操作 点,并创建REN#脉冲。

自动生成状态0(s0),并会持续一个IFCLK周期(20.83ns)。

因此,REN#在20.83ns时间内有效(图47)。

图47.REN#在一个时钟内有效

3.在OE#带内,将一个操作点放置在S0的右边界上,并在离它后面一个时钟的位置上放置另一个操作点。

这样,在完成状态S0后,可自动取消确认OE#并创建持续一个IFCLK周期的S1(20.83ns)状态。

图48.OE#在一个时钟内有效 文档编号.001-92462版本.*

A 28 EZ-USB®FX2LP™GPIF入门

4.通过点击时钟终端s1上的状态带来添加一个决策点(DP)状态。

从而创建状态S2,并会弹出“SpecifyDecision Point”对话框。

按照图49配置该决策点,为了无条件转换到闲置状态。

这时,您的波形将如图50所示。

图49.无条件转换到闲置状态 图50.添加了状态s2

5.最后需要进行的调整。

必须在S2期间采样(读)数据。

要想采样该数据,需要将操作点放置在S2状态的开始和结束的数据带上。

请注意,由于当前是在SingleRead(单读)选项卡中进行操作,因此高电平对应于采样,而不是驱动数据带。

最后,单个字读波形如图51所示。

6.通常,您应该将GPIFDesigner项目文件(*.gpf)和它生成的C文件存储在您的Keil项目文件夹内。

在这个范例中,它们已经作为本应用笔记的代码显示在该文件夹内。

文档编号.001-92462版本.*

A 29 图51.最后单个字读波形 EZ-USB®FX2LP™GPIF入门 9.3单个字操作的固件编程 在GPIFDesigner中实现单字操作波形后,需要将USB固件与GPIFDesigner输出集成在一起。

这样可以通过USB对外部FIFO进行读写操作。

开始对现有的固件框架项目进行操作并且添加GPIF管理代码。

双击Keil项目文件FX2_to_extsyncFIFO.uv2.该文件打开时,将出现Files(文件)面板,如图52。

表2介绍了这些文件。

图52.“FX2_to_extsyncFIFO”项目文件 已经将periph.c重命名为FX2_to_extsyncFIFO.c。

在该文件内,将USB端点和GPIF初始化代码添加到TD_Init()函数内,并将GPIF管理代码添加到TD_Poll()函数内。

表

2.项目文件说明 文件fw.cEzusb.libUSBJmpTb.OBJDscr.a51FX2_to_extsyncFIFO.c(由periph.c重命名得到)Gpif.c 说明固件框架用于处理USB请求,并调用任务调度程序TD_Poll()。

处理暂停、恢复、I2C等操作的函数集。

USB(INT2)和GPIF/从设备FIFO(INT4)中断源的中断矢量跳转表。

将EP2OUT和EP6IN作为FX2LP器件可用端点报告的FIFO示例器件描述符表。

可在这里找到TD_Poll()和TD_Init()的主用户应用代码。

您需要修改该文件,并不更新fw.c。

包含了执行单/FIFOGPIF操作波形特性的GPIF波形描述符表的文件。

它是从GPIFDesigner工具导出的C文件。

文档编号.001-92462版本.*

A 30 EZ-USB®FX2LP™GPIF入门 9.4 9.4.1 代码段 TD_Init()TD_INIT()进行下列操作: ▪将CPU时钟速度切换到48MHz(加电状态时默认速度为12MHz)▪将EP2配置为批量OUT端点,大小为512缓存的4倍▪将EP6配置为批量IN端点,大小同样为512缓存的4倍▪将FIFO配置为手动模式的字操作▪使用FIFORESET寄存器复位这些端点,并使EP2OUT端点确保可以接收USB主机(PC)中的数据 voidTD_Init(void) // { //settheCPUclockto48MHz CPUCS=((CPUCS&~bmCLKSPD) SYNCDELAY; Calledonceat|bmCLKSPD1); startup EP2CFG=0xA0;SYNCDELAY;EP4CFG=0x00;SYNCDELAY;EP6CFG=0xE0;SYNCDELAY;EP8CFG=0x00;SYNCDELAY; //EP2OUT,bulk,size512,4xbuffered//EP4notvalid//EP6IN,bulk,size512,4xbuffered//EP8notvalid EP2FIFOCFG=0x01;//manualmode,disablePKTENDzerolengthsend,wordops SYNCDELAY;EP6FIFOCFG=0x01;//manualmode,disablePKTENDzerolengthsend,wordopsSYNCDELAY; FIFORESET=SYNCDELAY;FIFORESET=SYNCDELAY;FIFORESET=SYNCDELAY;FIFORESET=SYNCDELAY; 0x80;0x02;0x06;0x00; //setNAKALLbittoNAKalltransfersfromhost//resetEP2FIFO//resetEP6FIFO//clearNAKALLbittoresumenormaloperation //outendpointsdoeuparmed//becauseEP2OUTisquadbuffered,writedummybytecountsfourtimes EP2BCL=0x80;SYNCDELAY;EP2BCL=0x80;SYNCDELAY;EP2BCL=0x80;SYNCDELAY;EP2BCL=0x80; //armEP2OUTbywritingbytecountw/skip. 文档编号.001-92462版本.*

A 31 EZ-USB®FX2LP™GPIF入门 SYNCDELAY; GpifInit();//initializeGPIFregisters ▪然后,TD_Init将调用位于gpif.c中的函数GPIFInit()。

▪GPIFInit()将GPIF波形描述符表加载到片上存储器内,并对其他GPIF寄存器进行配置。

▪每次只能加载四种波形。

如果描述物理接口操作所需的波形超过了四种,则必须手动加载另外一套四种波形。

▪IFCONFIG寄存器通过定义物理接口的GpifInit()函数被配置。

▪TD_Init()通过脉冲PA2(RS#)复位外部FIFO,如下面代码段中所示。

这样可确保在启动数据操作前已经初始化外 部FIFO。

//resettheexternalFIFO OEA|=0x04; //turnonPA2asoutputpin IOA|=0x04; //pullPA2highinitially IOA&=0xFB; //bringPA2low EZUSB_Delay

(1);//keepPA2lowfor~1ms,morethanenoughtime IOA|=0x04; //bringPA2high ▪在下面的代码中定义了USB供应商指令0xB2。

它允许主PC通过发出供应商指令复位外部FIFO。

BOOLDR_VendorCmnd(void){switch(SETUPDAT[1]) {caseVX_B2: {//resettheexternalFIFO OEA|=0x04; //turnonPA2asoutputpin IOA|=0x04; //pullPA2highinitially IOA&=0xFB; //bringPA2low EZUSB_Delay

(1);//keepPA2lowfor~1ms,morethanenoughtime IOA|=0x04; //bringPA2high *EP0BUF=VX_B2;EP0BCH=0;EP0BCL=1;EP0CS|=bmHSNAK; break;} //Armendpointwith#bytestotransfer//Acknowledgehandshakephaseofdevicerequest 文档编号.001-92462版本.*

A 32 EZ-USB®FX2LP™GPIF入门 9.4.2 触发GPIF单个字写操作 ▪8051代码通过访问XGPIFSGLDATH、XGPIFSGLDATLX和XGPIFSGLDATLNOX寄存器触发单个字读/单个字写GPIF波形。

从而启动数据传输。

▪为了触发GPIF单个字写操作,您需通过以下方式写入XGPIFSGLDATH和XGPIFSGLDATLX: XGPIFSGLDATH=

▪在本示例中,该操作是在GPIF_SingleWordWrite()函数内执行的。

该函数把一个字的值作为输入参数使用,并触发GPIF单字写操作。

voidGPIF_SingleWordWrite(WORDgdata){while(!

(GPIFTRIG&0x80))//pollGPIFTRIG.7Donebit {; } //usingregistersinXDATAspaceXGPIFSGLDATH=gdata;XGPIFSGLDATLX=gdata>>8; Writetransaction} //triggerGPIFSingleWord 9.4.3 ▪该函数在启动操作前通过轮询位GPIFTRIG.7检查GPIF是否处于IDLE(闲置)状态(如果GPIF状态机为闲置状态,将设置该位)。

在启动任何一个GPIF操作前,都必须始终确保GPIF处于闲置状态。

▪请注意单个操作寄存器的访问顺序,因为端点缓冲区是以FIFO形式进行组织的。

这样的顺序可确保端点缓冲区的第一个字节在FD[7:0]被写出,第二个字节在FD[15:8](低位优先格式)被写出。

GPIF单字读操作 ▪通过从XGPIFSGLDATX寄存器执行虚拟读,可以触发GPIF单个字读操作。

该读操作并没有进行任何数据传输,它仅启动了GPIF波形。

检测GPIFDONE位后,8051将读取XGPIFSGLDATH和XGPIFSGLDATLNOX寄存器中的字量。

▪在本示例中,此操作是在GPIF_SingleWordRead()函数内执行的。

该函数把目标变量的字指针作为参数使用,并执行GPIF单字读操作: voidGPIF_SingleWordRead(WORDxdata*gdata) { staticBYTEg_data=0x00; //dummyvariable while(!

(GPIFTRIG&0x80)){;} //pollGPIFTRIG.7Donebit //usingregisterinXDATAspace g_data=XGPIFSGLDATLX; //dummyreadtotriggerGPIF //SingleWordReadtransaction 文档编号.001-92462版本.*

A 33 EZ-USB®FX2LP™GPIF入门 while(!

(GPIFTRIG&0x80)){;} //pollGPIFTRIG.7Donebit 9.4.4 //usingregister(s)inXDATAspace,retrievewordjustreadfromext.FIFO*gdata=((WORD)XGPIFSGLDATLNOX<<8)|(WORD)XGPIFSGLDATH; } ▪该函数会先确保GPIF处于闲置状态,然后才从XGPIFSGLDATLX执行虚拟读,以触发GPIF单字读操作。

然后,在读取包含了字值的寄存器前,它会等待完成GPIF的执行。

TD_Poll() ▪位于函数TD_Poll()内的主应用代码会在器件操作期间被连续调用。

▪在此函数中,要调用GPIF_SingleWordWrite()和GPIF_SingleWordRead()函数。

▪GPIF_SingleWordWrite()将EP2OUT中的数据发送到外部FIFO,而GPIF_SingleWordRead()会读取外部FIFO 中的数据,并将结果写入到EP6IN内。

▪处理USBOUT传输的代码如下: if(!

(EP2468STAT&bmEP2EMPTY)&&(EXTFIFONOTFULL)){ //ifhostsentdatatoEP2OUTANDexternalFIFOisnotfull, Tcount=(EP2BCH<<8)+EP2BCL;//loadtransactioncountwithEP2byte count Tcount/=2; //divideby2forwordwidetransaction Source=(WORD*)(&EP2FIFOBUF); for(i=0x0000;i

这样可以确保外部FIFO中有足 够的空间用于存储从EP2OUT传输来的数据。

8051通过访问GPIFREADYSTAT寄存器检查GPIFRDY信号的状态。

EXTFIFONOTFULL是GPIFREADYSTAT的宏,它同bmBIT1进行AND运算。

▪如果EP2OUT端点中有数据,并且外部FIFO未满,那么字变量Tcount将使用计数值初始化。

通过访问EP2BCH/L寄存器,可以查看从主机传输到EP2OUT的字节数量。

每个GPIF单字写操作都会将一个字发送至外部FIFO,因此,操作数始终是端点缓冲区实际包含字节数的一半。

▪然后,“Forloop”语句以“Tcount”的次数调用GPIF_SingleWordWrite函数,并索引端点缓冲区EP2值,这样是为每次能以一字的方式向外部FIFO发送数据。

每个循环都会触发一个GPIF单写操作,因此每次将一个字的数据发送到外部FIFO。

▪传输“Tcount”字的数据后,将重新激活EP2端点,以便可以接受主机中的下个USB数据包。

FX2LP会自动否认所有OUT数据包,直到可以接收新的数据包为止。

因此,主机需要连续重试OUT传输。

文档编号.001-92462版本.*

A 34 EZ-USB®FX2LP™GPIF入门 ▪处理USBIN传输的代码如下: if(in_enable)//ifINtransfersareenabled,{ if(!

(EP2468STAT&bmEP6FULL)&&(EXTFIFONOTEMPTY)){ //ifEP6INisnotfullANDthereisdataintheexternal FIFO, Destination=(WORD*)(&EP6FIFOBUF); for(i=0x0000;i

从而触发一个GPIF字读取,并将该结果存储在目标地址中(该地址被设置为EP6INFIFO)。

每个重复次数都会递增目标地址,从而将在外部FIFO中检索到的字节填充到EP6INFIFO内。

▪将外部FIFO数据填充到EP6INFIFO后,8051代码会通过使能EP6IN端点将数据传输到主机PC。

使能前,FX2LPUSB逻辑会自动否认EP6的所有主机IN请求。

8051代码通过写入一个字节数(表示主机IN传输的字节数量)使能IN端点。

由于每个GPIF单字读操作接收外部FIFO中包含的两字节的整个字,因此,发送至主机的字节数始终是GPIF操作数的两倍。

▪通过将相应的值分配给“in_enable”标志,可以使能或禁用IN传输。

本示例定义了两条供应商指令,一个使能IN传输,另一个禁用IN传输,如下面代码所示: caseVX_B3://enableINtransfers{in_enable=TRUE;*EP0BUF=VX_B3;EP0BCH=0;EP0BCL=1;EP0CS|=bmHSNAK;break; }caseVX_B4://disableINtransfers{ 文档编号.001-92462版本.*

A 35 EZ-USB®FX2LP™GPIF入门 9.5 9.5.1 in_enable=FALSE;*EP0BUF=VX_B4; EP0BCH=0;EP0BCL=1;EP0CS|=bmHSNAK;break;} ▪IN供应商指令0xB3通过将in_enable设置为TRUE(真)来使能IN传输。

▪IN供应商指令0xB4通过将in_enable设置为FALSE(假)来禁用IN传输。

▪in_enable的默认值为FALSE。

▪通过in_enable标志您可以对每一次读写操作单独进行测试。

如果它始终被使能,那么将立即在OUT传输代码后 处理IN传输代码。

通过单步处理该代码,您可轻松捕获使用逻辑分析仪的每个读/写操作(适用于调试目的)。

运行GPIF单个字操作示例 不存在外部FIFO如果您尚未构建包含外部FIFO的FX2LP开发板,您同样能够使用示波器来观察GPIF写传输。

这样可以验证将数据从PC传输到FX2LP芯片的USB代码,以及将数据输出到外部FIFO的GPIF波形。

1.通过探针FX2LP开发板上的P2-11观察CTL0=WEN#,并且通过探针P1-19观察FIFO数据总线D0。

2.启动USB控制中心。

将FX2LP开发板插入到主PC端口内,该端口应该作为USB加载程序器件(如图21所示) 进行枚举。

否则,按照进入图21的各步骤进行操作。

3.请依次选择ProgramFX2>RAM并找到FX2_to_extsyncFIFO.hex文件以加载它。

4.展开Bulkloop器件并选择Bulkoutendpoint(0x02)。

5.在Datatosend(Hex)文本框内输入图53中显示的数字。

6.点击TransferData-OUT按键。

图53.USB控制中心传输数据

7.右下角中的文本窗口可确认该传输,并且应该在WEN#脉冲的下降沿上触发该示波器(图54). 文档编号.001-92462版本.*

A 36 图54.顶部:WEN#,底部:FD[0] EZ-USB®FX2LP™GPIF入门 9.5.2 9.6 9.6.1 请注意,第一个FIFO写传输会将FD[0]置于高电平,第二个写传输会将FD[0]置于低电平。

这样可以确保16位字按从低到高的顺序输出;第一字为0001,第二字为0100。

存在外部FIFO如果您已经编译好并将外部FIFO添加到开发板上,请先通过传输USB数据OUT测试该环回,如前面所述。

然后,使用同一个字节数进行传输数据IN操作。

本测试使用的是包含512个数据字节的512_count.hex文件。

1.在树状图中选择Bulkoutendpoint(0x02)(批量输出端点(0x02))。

单击DataTransferstab(数据传输)选项卡。

按下TransferFile-OUT按键,并选择Keil项目文件夹:FX2LPSourcecodeandGPIFprojectfiles\Firmware\FX2_to_extsyncFIFOGPIFSingleTransactions中的512_count.hex文件.点击Open,将512个字节发送到外部FIFO。

2.要想使用IN传输从外部FIFO中读回512个字节,必须使用一个USB供应商请求将in_enable标志设置为真。

在树状图中选择Controlendpoint(0x00);在Reqcode字段中输入‘0xB3’。

将ReqType设置为‘Vendor’,将Direction设置为‘In’,并将BytestoTransfer设置为‘1’。

点击TransferData。

3.在树状图中选择Bulkinendpoint(0x86)(批量输入端点(0x86))。

请确保BytestoTransfer中的字节数量为512。

按下TransferData-IN按键。

现在您可以看到从设备FIFO回读的512个字节。

单个字操作的逻辑分析仪波形 本节显示了GPIF引擎为GPIFDesigner定义的波形生成的时序。

单个字写波形 图55.单个字写波形 文档编号.001-92462版本.*

A 37 EZ-USB®FX2LP™GPIF入门 9.6.2 图55显示了GPIF引擎为GPIFDesigner定义的单写波形生成的时序信号。

本文档介绍了所有信号,包括GSTATE[2:0],该信号显示了GPIF引擎循环在执行单写操作时循环所经过的状态。

调试提示: ▪将GSTATE信号突出显示为逻辑分析仪标题时,您可以通过使用物理接口上生成的信号来确认GPIFDesigner波形。

这样还能够为调试流程提供辅助,因为您可以验证状态切换的正确性。

▪S0将数据放置在总线(PORTB为FD[7:0],PORTD为FD[15:8])上,并确认CTL0(连接至外部FIFO的WEN#线)。

该操作可将16位数据值写入到外部FIFO内。

▪请注意,需要为IFCLK上升沿提供足够的数据设置时间,因为外部FIFO的最小设置时间为4ns(请参见CY7C4265数据手册)。

▪S1是一个决策点状态,自动转至闲置状态,以终止该操作。

▪如果不存在无条件转移,那么在达到闲置状态(S7)之前,GPIF引擎将依次经过其余的所有状态(S2-S6)。

▪对于在批量OUT传输中写出的每个字,您应看到GPIF引擎按S0、S1和S7的顺序循环。

▪为捕获波形,请触发位于CTL0下降沿的逻辑分析仪。

▪4ns的采样频率将为您提供与图55所示波形的分辨率。

单个字读波形 图56.单个字读波形 图56显示的是GPIF引擎为GPIFDesigner定义的单个字读波形生成的时序。

本文档介绍了所有信号,其中包括了GSTATE[2:0],该信号显示了GPIF引擎循环在执行单读操作时循环所经过的状态。

调试提示: ▪S0确认CTL1(连接至外部FIFO的REN#线),S1确认CTL2(连接至外部FIFO的OE#线),S2对数据总线进行采样(PORTB为FD[7:0],PORTD为FD[15:8])。

该操作可将16位数据值写入到外部FIFO内。

▪请注意,需要为IFCLK上升沿提供足够的数据设置时间,因为GPIF的最小设置时间为9.2ns(请参见FX2LP数据手册)。

▪S2是一个决策点状态,自动转至闲置状态,以终止该操作。

▪如果没有无条件转移,达到闲置状态(S7)之前,GPIF引擎将依次经过其余所有状态(S3-S6)。

▪对于从批量IN传输中的外部FIFO读取的每个字,您都应看到GPIF引擎按S0、S1、S2和S7的顺序循环。

文档编号.001-92462版本.*

A 38 EZ-USB®FX2LP™GPIF入门 10 10.1 10.210.3 11 ▪为捕获波形,请触发位于CTL1下降沿的逻辑分析仪▪4ns的采样频率将为您提供与图56中的波形显示一样的分辨率。

相关文档 ▪FX2LP™入门:该文档可帮助新用户熟悉FX2LP。

▪FX2LP技术参考手册:本文档作为FX2LP的技术指南使用。

“通用可编程接口(GPIF)”章节对GPIF进行了详 细说明。

▪GPIFDesigner工具用户指南:为打开该文件,需要下载GPIFDesigner中的工具。

安装后,请依次选择Help>ThisTool. ▪EZ-USBFX1-EZ-USBFX2LPDevelopmentKitQuickStartGuide.pdf(EZ-USBFX1-EZ-USBFX2LP开发套件快速入门指南)和EZ-USBDevelopmentKitUserGuide.pdf(EZ-USB开发套件用户指南):这两个文档介绍的都是如何使用CY3684套件,(安装DVK后)C:\Cypress\USB\CY3684_EZUSB_FX2LP_DVK\1.0\Documentation中找到。

▪EZ-USBFX1/FX2LP的端点架构:通过本应用笔记可以了解FX1/FX2LP中的数据流。

其他GPIF示例 可以在下面各赛普拉斯应用笔记中查找更多GPIF示例: ▪AN57322:通过GPIF将SRAM连接至FX2LP:该应用笔记介绍的是如何使用一个GPIF8位异步(无时钟)接口将CY7C1399BSRAM连接至FX2LP。

它还介绍了将FX2LP连接至其它SRAM的指导信息。

▪AN63787:使用8位异步接口的EZ-USBFX2LPGPIF和从设备FIFO配置示例:本应用笔记描述了如何在手动模式和自动模式下配置EZ-USBFX2LP中的通用可编程接口(GPIF)和从设备FIFO,以执行8位异步并行接口。

通过使用两个互联的FX2LP开发板(一个作为GPIF主设备使用,另一个作为GPIF从设备使用)可以测试该设计。

▪AN4051:UDMA的FX2LPGPIF流状态特性:该应用笔记介绍了GPIF的“流状态”特性。

该特性扩展了GPIF的性能,以处理ATAPIUDMA。

参考设计 ▪CY4611B—USB2.0USB到ATA参考设计:流行的FX2LP应用就是USB批量存储器。

通过FX2LPGPIF可以轻松连接至附加驱动。

赛普拉斯提供了一个使用FX2LP的完整批量存储器参考设计。

数据手册 ▪EZ-USBFX2LPUSB微控制器高速USB外设控制器▪CY7C4265数据手册 总结 本应用笔记是用于介绍EZ-USBFX2LPGPIF的文档。

它说明了创建一个通用的可编程接口的操作步骤,并提供了用于描述GPIFDesigner主要特性的各种示例。

文档编号.001-92462版本.*

A 39 EZ-USB®FX2LP™GPIF入门 文档修订记录 文档标题:AN66806-EZ-USB®FX2LP™GPIF入门文档编号:001-92462 修订版***

A ECN43768685880686 原始变更LISZSXFS 提交日期08/29/201409/12/2017 变更说明本文档版本号为Rev**,译自英文版001-66806Rev*

D。

本文档版本号为Rev*

A,译自英文版001-66806Rev*

G. 文档编号.001-92462版本.*

A 40 EZ-USB®FX2LP™GPIF入门 全球销售和设计支持 赛普拉斯公司拥有一个由办事处、解决方案中心、厂商代表和经销商组成的全球性网络。

要找到离您最近的办事处,请访问赛普拉斯所在地。

产品 ARM®Cortex®微控制器汽车级产品时钟与缓冲器接口物联网存储器微控制器PSoC电源管理IC触摸感应USB控制器无线连接 /arm/automotive/clocks/interface/iot/memory/mcu/psoc/pmic/touch/usb/wireless PSoC®解决方案 PSoC1|PSoC3|PSoC4|PSoC5LP|PSoC6 赛普拉斯开发者社区 论坛|WICEDIOT论坛|项目|视频|博客|培训|组件 技术支持 /support Allothertrademarksorregisteredtrademarksreferencedhereinarethepropertyoftheirrespectiveowners. CypressSemiconductor198ChampionCourtSanJose,CA95134-1709 ©赛普拉斯半导体公司,2011-2017年。

本文件是赛普拉斯半导体公司及其子公司,包括SpansionLLC(“赛普拉斯”)的财产。

本文件,包括其包含或引用的任何软件或固件(“软件”),根据全球范围内的知识产权法律以及美国与其他国家签署条约由赛普拉斯所有。

除非在本款中另有明确规定,赛普拉斯保留在该等法律和条约下的所有权利,且未就其专利、版权、商标或其他知识产权授予任何许可。

如果软件并不附随有一份许可协议且贵方未以其他方式与赛普拉斯签署关于使用软件的书面协议,赛普拉斯特此授予贵方属人性质的、非独家且不可转让的如下许可(无再许可权)

(1)在赛普拉斯特软件著作权项下的下列许可权(一)对以源代码形式提供的软件,仅出于在赛普拉斯硬件产品上使用之目的且仅在贵方集团内部修改和复制软件,和(二)仅限于在有关赛普拉斯硬件产品上使用之目的将软件以二进制代码形式的向外部最终用户提供(无论直接提供或通过经销商和分销商间接提供),和

(2)在被软件(由赛普拉斯公司提供,且未经修改)侵犯的赛普拉斯专利的权利主张项下,仅出于在赛普拉斯硬件产品上使用之目的制造、使用、提供和进口软件的许可。

禁止对软件的任何其他使用、复制、修改、翻译或汇编。

在适用法律允许的限度内,赛普拉斯未对本文件或任何软件作出任何明示或暗示的担保,包括但不限于关于适销性和特定用途的默示保证。

没有任何电子

设备是绝对安全的。

因此,尽管赛普拉斯在其硬件和软件产品中采取了必要的安全措施,但是赛普拉斯并不承担任何由于使用赛普拉斯产品而引起的安全问题及安全漏洞的责任,例如未经授权的访问或使用赛普拉斯产品。

此外,本材料中所介绍的赛普拉斯产品有可能存在设计缺陷或设计错误,从而导致产品的性能与公布的规格不一致。

(如果发现此类问题,赛普拉斯会提供勘误表)赛普拉斯保留更改本文件的权利,届时将不另行通知。

在适用法律允许的限度内,赛普拉斯不对因应用或使用本文件所述任何产品或电路引起的任何后果负责。

本文件,包括任何样本设计信息或程序代码信息,仅为供参考之目的提供。

文件使用人应负责正确设计、计划和测试信息应用和由此生产的任何产品的功能和安全性。

赛普拉斯产品不应被设计为、设定为或授权用作武器操作、武器系统、核设施、生命支持设备或系统、其他医疗设备或系统(包括急救设备和手术植入物)、污染控制或有害物质管理系统中的关键部件,或产品植入之设备或系统故障可能导致人身伤害、死亡或财产损失其他用途(“非预期用途”)。

关键部件指,若该部件发生故障,经合理预期会导致设备或系统故障或会影响设备或系统安全性和有效性的部件。

针对由赛普拉斯产品非预期用途产生或相关的任何主张、费用、损失和其他责任,赛普拉斯不承担全部或部分责任且贵方不应追究赛普拉斯之责任。

贵方应赔偿赛普拉斯因赛普拉斯产品任何非预期用途产生或相关的所有索赔、费用、损失和其他责任,包括因人身伤害或死亡引起的主张,并使之免受损失。

赛普拉斯、赛普拉斯徽标、Spansion、Spansion徽标,及上述项目的组合,WICED,及PSoC、CapSense、EZ-USB、F-RAM和Traveo应视为赛普拉斯在美国和其他国家的商标或注册商标。

请访问获取赛普拉斯商标的完整列表。

其他名称和品牌可能由其各自所有者主张为该方财产。

文档编号.001-92462版本.*

A 41

声明:

该资讯来自于互联网网友发布,如有侵犯您的权益请联系我们。